引 言

射頻識別(Radio Frequency Identification,RFID)技術(shù)是一種新興的非接觸式自動識別技術(shù),在工業(yè)自動化、商業(yè)自動化、交通運輸控制管理、防偽及軍事等眾多領(lǐng)域都有廣泛的應(yīng)用前景。它利用無線射頻方式進(jìn)行非接觸雙向數(shù)據(jù)通信,以達(dá)到目標(biāo)識別并交換數(shù)據(jù)的目的,可用來跟蹤并管理幾乎所有的物理對象。RFID電子標(biāo)簽已經(jīng)成為21世紀(jì)全球自動識別技術(shù)發(fā)展的主要方向。目前,RFID已經(jīng)得到了廣泛應(yīng)用,且有國際標(biāo)準(zhǔn)ISO10536,ISO14443,ISO15693,ISO18000,EPC Global等幾種。其中,ISO18000-6C屬于超高頻射頻識別技術(shù)標(biāo)準(zhǔn),它融合了EPC C1G2標(biāo)準(zhǔn)。該標(biāo)準(zhǔn)的特點是速度快,可以同時讀取的標(biāo)簽數(shù)量多,理論上能讀到1 000多個標(biāo)簽;功能強,具有多種寫保護(hù)方式;安全性強。

在我國,由于射頻識別技術(shù)起步較晚,應(yīng)用的領(lǐng)域不是很廣,主要的應(yīng)用是基于中低頻的應(yīng)用,包括車輛管理、門禁管理等。目前,超高頻射頻識別技術(shù)及其應(yīng)用在我國正處于初級發(fā)展階段,國內(nèi)目前還沒有成熟的超高頻電子標(biāo)簽芯片設(shè)計技術(shù)。

在此,首先介紹電子標(biāo)簽的工作原理及ISO18000-6C標(biāo)準(zhǔn),并根據(jù)ISO18000-6C標(biāo)準(zhǔn),設(shè)計了實現(xiàn)超高頻電子標(biāo)簽驗證平臺的整體電路。重點討論基于EP1C6Q240FPGA的數(shù)字基帶部分設(shè)計與實現(xiàn)。最后給出了該平臺的測試結(jié)果,驗證了平臺設(shè)計的正確性和可靠性。

1 電子標(biāo)簽的工作原理

射頻識別系統(tǒng)通常由讀寫器(Reader)和射頻標(biāo)簽(RFID Tag)構(gòu)成。附著在待識別物體上的射頻標(biāo)簽內(nèi)存有約定格式的電子數(shù)據(jù),作為待識別物品的標(biāo)識性信息。讀寫器可無接觸地讀出標(biāo)簽中所存的電子數(shù)據(jù)或者將信息寫入標(biāo)簽,從而實現(xiàn)對各類物體的自動識別和管理。讀寫器與射頻標(biāo)簽按照約定的通信協(xié)議采用先進(jìn)的射頻技術(shù)互相通信,其基本通信過程如下。

(1)讀寫器作用范圍內(nèi)的標(biāo)簽接收讀寫器發(fā)送的載波能量,上電復(fù)位;

(2)標(biāo)簽接收讀寫器發(fā)送的命令并進(jìn)行操作;

(3)讀寫器發(fā)出選擇和盤存命令對標(biāo)簽進(jìn)行識別,選定單個標(biāo)簽進(jìn)行通信,其余標(biāo)簽暫時處于休眠狀態(tài);

(4)被識別的標(biāo)簽執(zhí)行讀寫器發(fā)送的訪問命令,并通過反向散射調(diào)制方式向讀寫器發(fā)送數(shù)據(jù)信息,進(jìn)入睡眠狀態(tài),此后不再對讀寫器應(yīng)答;

(5)讀寫器對余下標(biāo)簽繼續(xù)搜索,重復(fù)(3),(4)分別喚醒單個標(biāo)簽進(jìn)行讀取。直至識別出所有標(biāo)簽。

標(biāo)簽向讀寫器傳送數(shù)據(jù)是通過反向散射調(diào)制技術(shù),對于無源電子標(biāo)簽,其本身沒有足夠的發(fā)射能量,所以通過改變天線的匹配阻抗控制天線的反射強弱,阻抗不匹配時天線反射率很大,阻抗匹配時天線反射率很小,以此來表示輸出信號的有無。

2 ISO18000-6C標(biāo)準(zhǔn)

ISO18000-6c標(biāo)準(zhǔn)為:

工作頻率 標(biāo)簽應(yīng)能夠在860~960 MHz的頻率范圍內(nèi)接收從讀寫器發(fā)出的功率并能夠與讀寫器通信。

調(diào)制 讀寫器應(yīng)采用DSB-ASK,SSB-ASK或PR-ASK調(diào)制方式進(jìn)行通信。標(biāo)簽應(yīng)該能夠解調(diào)上述3種類型的調(diào)制。標(biāo)簽反向散射應(yīng)采用ASK或PSK調(diào)制。標(biāo)簽商選擇調(diào)制形式。讀寫器能夠解調(diào)上述2種調(diào)制。

數(shù)據(jù)編碼 讀寫器到標(biāo)簽的鏈路應(yīng)采用PIE編碼,標(biāo)簽將反射散射的數(shù)據(jù)編為該數(shù)據(jù)速率的副載波FMO基帶或Miller調(diào)制。讀寫器發(fā)出編碼選擇的命令。

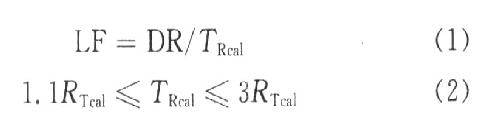

數(shù)據(jù)速率 讀寫器到標(biāo)簽的數(shù)據(jù)速率根據(jù)Tari值進(jìn)行選擇,數(shù)據(jù)速率可以從40~640 Kb/s。標(biāo)簽的反射速率由下面兩個公式共同決定:

3 RFID板級標(biāo)簽驗證平臺的總體設(shè)計與實現(xiàn)

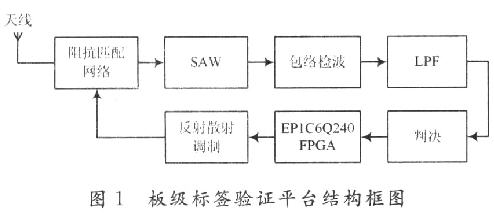

板級標(biāo)簽主要由模擬射頻和數(shù)字處理2部分組成。圖1為板級電子標(biāo)簽驗證平臺的結(jié)構(gòu)框圖。

模擬射頻部分采用分立元件實現(xiàn),完成射頻信號的接收,來自RFID讀寫器的信號通過天線和阻抗匹配網(wǎng)絡(luò),經(jīng)過915 MHz的聲表面濾波器濾波,進(jìn)行包絡(luò)檢波后,通過一個運放構(gòu)成的一階有源低通濾波器,再由電壓比較器完成高低電平的判決。數(shù)字部分由EP1C6Q240FPGA實現(xiàn),完成ISO18000-6C協(xié)議處理,EP1C6Q240FPGA接收來自前端的TTL電平,完成PIE解碼、CRC校驗、命令解析、狀態(tài)轉(zhuǎn)移、數(shù)據(jù)存儲、FMO編碼等功能。FMO編碼通過反相散射調(diào)制輸出,改變天線的反射阻抗實現(xiàn)。

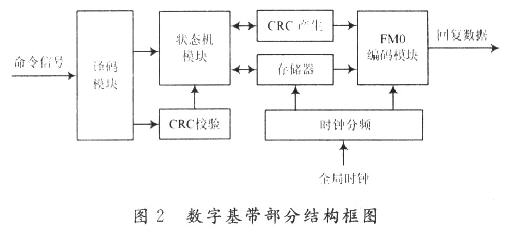

數(shù)字基帶部分的設(shè)計在Altera公司的EP1C6Q240FPGA上實現(xiàn)。經(jīng)過對協(xié)議內(nèi)容的深入研究,實現(xiàn)標(biāo)簽數(shù)字部分采用Top-down的設(shè)計方法,首先對電路功能進(jìn)行詳細(xì)描述,按照功能對整個系統(tǒng)進(jìn)行模塊劃分;再用Vexilog硬件描述語言進(jìn)行RTL代碼設(shè)計。數(shù)字基帶結(jié)構(gòu)框圖如圖2所示,它包括譯碼模塊、循環(huán)冗余校驗(Cyclic Redundancy Check,CRC)校驗?zāi)K、狀態(tài)機模塊、CRC產(chǎn)生模塊、存儲器、編碼模塊和時鐘分頻模塊。譯碼模塊接收模擬部分解調(diào)出的命令信號,根據(jù)協(xié)議中規(guī)定的命令格式將信號譯碼成標(biāo)簽數(shù)字部分可識別的二進(jìn)制數(shù)據(jù),并發(fā)送到CRC校驗?zāi)K和狀態(tài)機模塊。CRC校驗?zāi)K對收到的命令進(jìn)行完整性校驗,若確認(rèn)為有效命令,則觸發(fā)狀態(tài)機模塊,控制標(biāo)簽執(zhí)行相應(yīng)操作,如讀寫存儲器、防沖突控制等。處理完成后,則將要發(fā)送的數(shù)據(jù)送至CRC:產(chǎn)生模塊產(chǎn)生相應(yīng)的CRC校驗碼,然后將要發(fā)送的數(shù)據(jù)和校驗碼一起送至編碼模塊,最后由編碼模塊以特定的脈沖形式發(fā)送給模擬部分進(jìn)行處理后,再采用射頻技術(shù)發(fā)送給讀寫器。

4 測試結(jié)果

QuartusⅡ6.0是Altera FPGA/CPLD的綜合性集成設(shè)計平臺。該平臺集成了設(shè)計輸入、仿真、邏輯綜合、布局布線與實現(xiàn)、時序分析、芯片下載與配置、功率分析等幾乎所有設(shè)計流程所需的工具。Verilog HDL程序在QuartusⅡ6.O環(huán)境下編譯、仿真和下載,板級標(biāo)簽經(jīng)過總體設(shè)計、PCB板設(shè)計與實現(xiàn)、代碼設(shè)計、仿真與下載,以及系統(tǒng)調(diào)試后,能夠與支持ISO18000-6C標(biāo)準(zhǔn)的讀寫器(Cetc7 Rlid Reader V 1.O)進(jìn)行通信,快速準(zhǔn)確地收發(fā)信息,并實現(xiàn)防沖突功能。圖3顯示板級標(biāo)簽?zāi)軌蚪獯a來自閱讀器的命令信息,在狀態(tài)機的控制下,正確地輸出FM0編碼信號。圖4顯示板級標(biāo)簽?zāi)軌蛑С諭SO18000-6C標(biāo)準(zhǔn)的閱讀器正確讀取(讀取到的EPC碼與標(biāo)簽一致),讀取效果良好(73次/10 s),讀取性能穩(wěn)定。測試表明,板級標(biāo)簽?zāi)軌驅(qū)崿F(xiàn)ISO18000-6C標(biāo)準(zhǔn)中的讀寫功能,標(biāo)簽工作性能穩(wěn)定,可靠性都能達(dá)到預(yù)期的效果。

5 結(jié) 語

根據(jù)ISO18000-6C標(biāo)準(zhǔn),采用EP1C6Q240FPGA以及模擬射頻分立元件,經(jīng)過總體設(shè)計、PCB板設(shè)計與實現(xiàn)、代碼設(shè)計、仿真與下載,以及系統(tǒng)調(diào)試后,完成了基于FPGA的板級標(biāo)簽的軟、硬件設(shè)計與實現(xiàn)。該系統(tǒng)通過測試,已能夠正常工作,讀寫性能優(yōu)異,并實現(xiàn)了防沖突功能。在此基礎(chǔ)上可以進(jìn)一步提高其安全性和可靠性,所設(shè)計的標(biāo)簽數(shù)字電路RTL代碼能夠直接應(yīng)用到標(biāo)簽芯片開發(fā)中,為下一步設(shè)計出符合該標(biāo)準(zhǔn)的電子標(biāo)簽芯片提供了有力的保證。

作者:鄧方東,謝澤明,伍繼雄/華南理工大學(xué),中國電子科技集

粵公網(wǎng)安備 44030902003195號

粵公網(wǎng)安備 44030902003195號