3.3 調相模塊FPGA實現方法

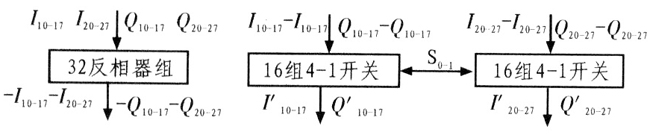

圖6給出數據調相電路組成的模塊.雙口RAM由FPGA來實現,由于FPGA的可編程邏輯,采樣數據I10-17,I20-27、Q10-17、Q20-27、數據調相器電路,輸入為I10-17,Q10-17,-I10-17,-Q10-17;輸出為,I10-17,Ql0-17,I10-17,Q10-17,-I10-17,-Q10-17;輸入輸出組合,由控制字Sn~S1的組合決定。設計采用了數字調相移頻的原理.通過連續改變數字移相器的相移使輸出信號載頻偏移設定值。該方法的移頻精度、穩定度取決于數字電路的時鐘精度和穩定度。

圖6 數據調相電路組成模塊

綜上所述,得到可控制的調頻調相干擾信號,進而優化了DRFM的干擾系統。DRFM本身是一種高速數字存儲器件.可以在滿足奈奎斯特采樣定理的條件下對截獲到的信號作長時間相參復制,如加入信號處理模塊就可以更靈活的產生干擾信號,使適當的干擾信號進入對方雷達接收設備,破壞對方雷達對目標回波信號的檢測,達到有效干擾的目的。而且此方法有很高的抗干擾特性.設計靈活,較易實現,不失為一種新的選擇。

4、結束語

本文主要分析在雷達干擾機中DRFM結構的工作原理。加入了一種信號調制模塊,該方法突破了傳統時間遲延的干擾效果。可更加靈活的產生滿足設計要求的干擾信號,達到有效干擾目的。并提出用FPGA方法數字調相,可簡單快捷達到干擾目的,優化DRFM的結構和干擾精度,為未來的電子戰設備提供有效的參考價值。

粵公網安備 44030902003195號

粵公網安備 44030902003195號