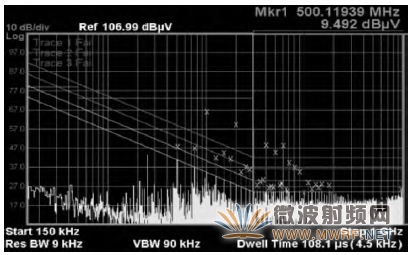

圖7 10MHz—ADC測試圖

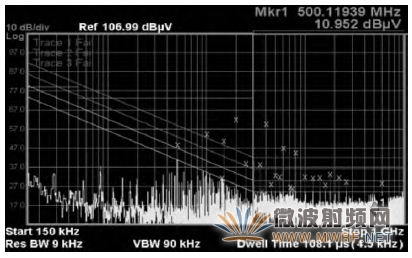

圖8 20MHz—ADC測試圖

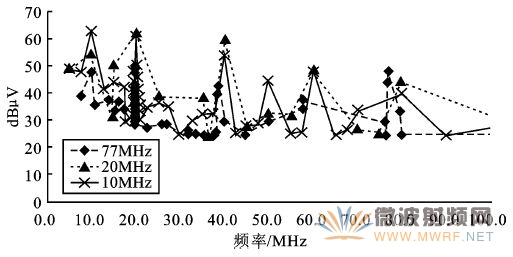

圖9 77MHz—ADC測試圖

圖10 10/20/77MHz—ADC測試數據整理

圖7、圖8、圖9分別是10MHz、20MHz和77MHz的測試圖,圖10是整理后的數據。通過對比可以得出,頻譜大致集中在100MHz以內,在對應工作時鐘的主頻點處干擾值最大,10MHz、20MHz情況下在相應倍頻點(如40MHz、60MHz等頻點)附近的干擾值也比較集中。

提取數據得到10 MHz時峰值點為9.999MHz(62.643dBμV),20 MHz 時的峰值點為20.002MHz(61.692dBμV),77MHz時的峰值點為19.264MHz(48.049dBμV)以及77.042MHz(47.316dBμV)。可以看出,77MHz時干擾強度和密度反而要弱于20MHz,可能是由于77MHz是MCU工作的極限時鐘,此時工作性能受到一定影響,導致測試的結果有所不同。

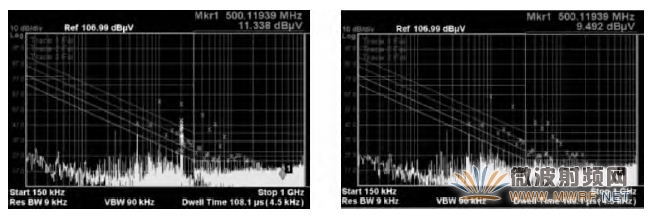

③由于汽車電子MCU的工作時鐘可以選擇外部晶振或者內部PLL倍頻,所以要對兩種情況分別測試,以便比較是否有差別。運行ADC程序后的測試結果如圖11所示。

圖11 PLL vs.外部晶振(10MHz)

從圖11中可以看出,在頻譜范圍內各個峰值點的分布大致相同,整個頻譜范圍內沒有明顯差異,MCU通過外部晶振或PLL倍頻兩種方式測得的結果基本一致,時鐘源選擇上不會對芯片的電磁干擾強度帶來影響。

3.3 150Ω測試

(1)設備裝置連接同1Ω測試法的步驟①;

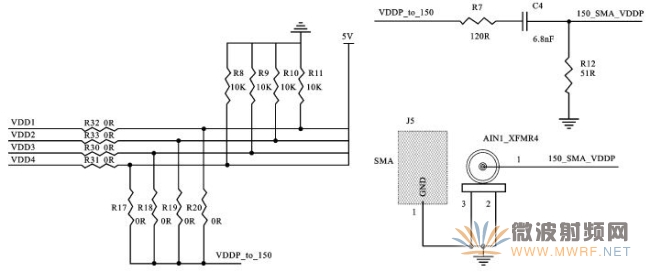

(2)根據芯片電源類型,電源分為4路,分別是VDD1(數字IO 供電的5V 電源信號)、VDD2(為ADC和PLL供電的LDO 的5V 電壓)、VDD3(數字邏輯LDO的5V電壓輸入)和VDD4(Flash的5V電壓輸入)。可單獨對每一路電源的干擾噪聲進行捕捉,連接方式與1Ω 測試法步驟②相同,如圖12所示;

圖12 VDD連接150Ω網絡145

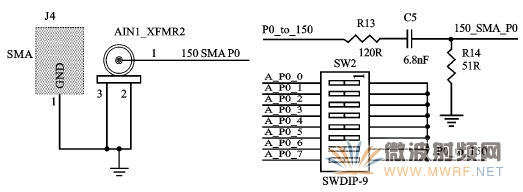

(3)根據汽車電子MCU應用特點,選取最為典型的PWM、CAN 程序,為了方便以后對眾多引腳進行單獨測量,將P0、P1、P2(P3未涉及到外設功能復用)端口共24個引腳進行了開關控制,再通過150Ω耦合網絡連接到EMI接收機,圖13是P0端口的電路原理圖,P1和P2的原理圖同P0。

圖13 IO-P0連接150Ω網絡

(4)重復測試多次,得到較多測試樣本,經過整理,下面是各個測試情況的說明。

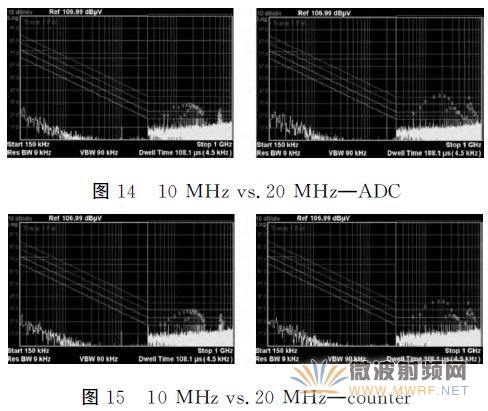

①從電源端口結果來看,區別很小,下面以VDD1為例進行分析說明。VDD1測試選取了ADC和counter(數字計數器)的程序,以比較不同類別的程序對數字供電是否有影響,測試結果如圖14、圖15所示。

在10MHz和20MHz時鐘上對比,ADC最高峰值分別為35.827dBμV、43.517dBμV;counter的最高峰值為35.899dBμV、43.271dBμV。可以得出頻率越高,干擾強度越大。但就兩類程序橫向對比來看,結果基本上一致。另外還發現60~300MHz和550~650MHz兩處集中的干擾頻譜,可見電源處的干擾在高頻附近比較明顯。

②PWM 功能測試

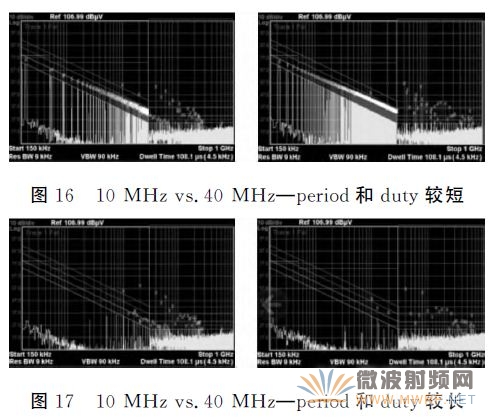

雙通道模式下,在不同占空比和周期大小情況下,測試對應P口引腳處傳導發射強度的大小,測試結果如圖16、圖17所示。

從圖16中的干擾密度可看出時鐘對電磁干擾影響程度。在圖17中,由于period和duty較長,測試結果相差不大,此時時鐘頻率變成次要因素,主要因素取決于輸出引腳處高低電平變化周期長短。

③CAN功能測試

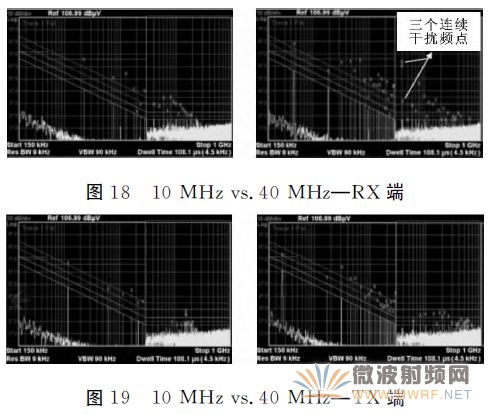

運行Loopback(回路模式)程序,在不同時鐘頻率下進行比較,測試結果如圖18、圖19所示。

從圖16~19中觀察,隨著時鐘頻率變大,TX和RX端口的傳導輻射強度也變大。對于RX端口,10/40MHz頻點附近的干擾密度比較大,且在40MHz時候現象更明顯,捕捉到連續三個頻點(圖18右側標注),分別是39.060 MHz(71.063dBμV)、39.360MHz(67.447dBμV)、40.020MHz(39.171dBμV),兩個時鐘下的峰值都在70~85dBμV 之間,但一般都在10MHz以下,應該是受低頻某一頻點的影響較明顯。

對于TX端口,10/40MHz頻點附近的干擾密度沒有RX明顯,峰值也都在70~85dBμV 之間,且發生在10MHz以下,和RX的特點大致相同。

4、測試結果分析

從測試數據結果可以總結出以下幾點:

①在時鐘頻率上,從10 MHz到40 MHz、77MHz,干擾強度或是密度在整體上都會增加,可以是一小段頻譜或者是整個頻譜范圍內,這與測試對象關系比較大。分析原因不難發現,由于時鐘電路產生的時鐘信號一般都是周期信號,其頻譜是離散的,離散譜的能量集中在有限的頻率上,又由于系統中各個部分的時鐘信號通常由同一時鐘分頻、倍頻得到,它們的譜線之間也是倍頻關系,會重疊起來進而增大輻射的幅值。

②在程序燒寫方式上,外部晶振或PLL倍頻兩種方式測得的結果基本一致,整個頻譜范圍內沒有明顯差異,時鐘源選擇上不會對芯片的電磁干擾強度帶來影響。

③從VDD1測試結果來看,除了得出頻率越高,干擾強度越大之外,還發現出現干擾的頻譜范圍分別在60~300MHz和550~650MHz兩處,可見電源處的干擾在高頻附近比較明顯。

④對于PWM 功能,通過配置輸出波形周期和占空比大小,會導致在不同時鐘下產生的電磁干擾強度有所差異。由于雙通道模式下寄存器為16bit(原單通道模式為8bit),此時周期和占空比可配置的數值變大,PWM 波輸出引腳處的高低電平翻轉周期就取決于周期和占空比的設置,與時鐘的關系變得沒有之前如此緊密,時鐘變成了次要因素。由此建議在滿足功能要求的前提下,使用PWM 功能時盡量將周期和占空比數值變得大一些,這樣會較好地改進EMC性能;

⑤對于CAN 總線來講,通過10 MHz和40MHz時鐘對比,當合理地降低時鐘工作頻率,會使一大段頻譜范圍內的干擾值降低,從整體上較好的控制EMI帶來的影響。

5、結束語

對于微電子行業來說,芯片級電磁兼容性的設計與測試已經成為一個非常重要的主題。實際上,如果不對集成電路電磁輻射及抗擾度方面進行深入的研究,就很難滿足電子設備電磁兼容性方面的需要。本文通過對設計方法的引入,并進一步通過測試方案去總結歸納影響電磁發射的因素和原因,從而間接證明了設計方法的必要性和重要性。

粵公網安備 44030902003195號

粵公網安備 44030902003195號