要點:

1、雖然每個小組可以優化局部功耗,但單個團隊不可能創建出一個低功耗設計。反之,任何一個小組都可能摧毀這種努力。

2、功率估計是一種精確的科學。但是,只有當你擁有了一個完整設計和一組正確的矢量后,這種概念才為真。

3、對任何問題而言,處理器通常是能效最低的方法,但因為它們具備了功能多重性,一般可以用最小面積獲得實現。

4、電源分配網絡應能夠在不損及電壓完整性的情況下,維持負載。

過去十年來,功率已經成為一個關鍵的設計考慮,并在工程師設計與驗證系統方面帶來了一些巨大的挑戰。物理學不再提供免費便車。

功率是能量被消耗的速率,這在十年前還不是熱門,但今天已是一個重要的設計考量。系統的能耗會帶來熱量、耗盡電池、增加電能分配網絡的壓力,并且加大成本。移動計算的發展最先推動了對降低能耗的期望,但能耗的效應現在已遠遠超出這個范圍,可能在業界帶來一些最大的結構性變化。對于服務器農場、云計算、汽車、芯片,以及依賴于能源獲取的泛在式傳感器網絡,這都是一個關鍵性問題。

突然改變的原因是,物理學已把工藝技術帶到了90nm以下尺度。但是,隨著結點尺寸越來越小,電壓降低,從而造成功率的相應下降。通常,即使開發人員增加了更多功能,功率預算也會保持不變。在更小尺度下,電壓的縮放更加困難,無法維持。當電壓接近于閾值電壓時,開關時間就會增加。為補償這一問題,設計人員會降低閾值電壓,但這樣做顯著增加了泄漏電流和開關電流。

設計流程中的每個階段都對功耗有影響,從軟件架構到器件物理。雖然每個小組都可以做局部的功耗優化工作,但沒有一個團隊可以單獨創建出一個低功耗設計。反之,任何一個團隊都可能摧毀低功耗的努力。這種狀況就產生了一種對協同與交叉學科工具的新需求。功率問題不再止于芯片。它們遍及互連結構、電路板與系統設計、電源控制器等諸方面。當前的EDA工具并非按功率概念而建立,這意味著設計人員要采用改進型方法,而不是從頭開始的新方法。

物理原理的角色

一只芯片消耗的功率是開關(或動態)功率和無源(或泄漏)功率之和。功率的動態成分源于設計的容性負載。當某個線網從0轉換到1時,這個成分通過一個PMOS晶體管充電。從電源獲得的能量等于容性負載與電壓平方的乘積。系統將這個能量的一半存儲在電容中;另一半則耗散在晶體管上。對于從1至0的轉換,不會從電源獲得更多能量,但電荷要耗散在NMOS晶體管上。假設結點以頻率F變化,則動態功率為FCLVDD2,其中,CL是容性負載,VDD是電壓。雖然也存在其它形式的動態功率,但它們要小得多。

由于電壓是平方項,因此降低電壓有相當顯著的效果。不幸的是,性能也與電壓相關,因為增加電壓會增加柵極的驅動VGS-VT,其中VGS是柵源電壓,VT是閾值電壓。使用較陳舊的技術時,泄漏功率并不明顯。但隨著器件尺度的減小,很多區域中的泄漏變得更加顯著,包括柵極氧化物隧穿、亞閾值電壓、反偏結點、柵極導致的漏極泄漏,以及因熱載流子注入而產生的柵極電流等。

二氧化硅是常用的絕緣材料。在低厚度水平下, 電子可以隧穿它。這種關系是指數型的,意味著厚度減半,泄漏增至四倍,在晶體管尺度降到130nm以下之前,這還不是一個問題。用高k電介質代替二氧化硅可以提供相近的器件性能,獲得更厚的柵級絕緣體,從而降低了這個電流。

晶體管有一個柵源閾值電壓,低于這個電壓時,通過器件的亞閾值電流就會呈指數倍下降。當降低電源電壓以減少動態功耗時,閾值電壓也減小,從而使柵極電壓擺幅低于器件關斷的閾值。亞閾值傳導會隨柵極電壓呈指數式變化。

在擴散區和阱之間,或在阱與基材之間的一個反偏構造,會產生小的反偏結泄漏。在MOS晶體管漏極結上的高電場效應會產生柵極導致的漏極泄漏,這通常要用制造技術來處理。柵極電流泄漏的原因是短溝道器件的閾值電壓漂移,并與器件中的高電場有關。對這個效應的控制主要也是靠制造技術。

設計人員要在動態功耗和靜態功耗之間做一個折中。降低電壓會減小動態功耗,但增加了靜態功耗。我們來看一只手機內的典型芯片。當器件工作時,泄漏要占所消耗功率的大約10%;其它90%是動態功耗。但當手機處于待機模式時(可能占到總時間的90%),芯片中的動態功耗就很少。因此,盡量減小兩種功耗有著相同的重要性。

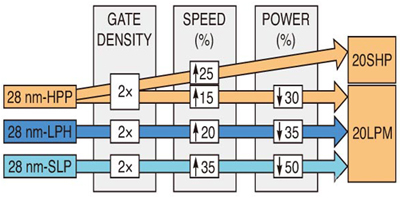

各種器件的功耗方面在持續地改進。例如,在相同頻率下,三星的28nm低功耗工藝比45nm低功耗工藝的動態功耗與待機功耗都減少了35%,與采用45nm低功耗的系統單芯片設計相比,28nm工藝在相同頻率下的動態功耗降低了60%。臺積電28nm高性能低功耗工藝的待機功耗要比其40nm低功耗工藝低40%以上。同時GlobalFoundries公司為其28nm結點提供了三種功率水平(圖1)。

圖1,臺積電的28-HPL工藝待機功耗較40-LP工藝低40%以上。而Global Foundries則為其28nm結點提供了三種功率水平

摩爾定律繼續有效,芯片在每個器件中封裝了更多功能。據Open-Silicon的營銷總監Colin Baldwin稱,客戶可以用近似的單位成本和兩倍的性能,設計出下一代器件,雖然總功耗會增加,但單只器件的功耗是下降的。時鐘頻率是另外一個緩慢上漲的變量,但在很多市場上增速都慢于工藝。Open-Silicon發現,大多數用戶試圖在略微增加總體功耗的情況下,集成更多的功能。因此,要維持相同的總功耗,就要看設計流程的其它部分中可以節省的能耗。

粵公網安備 44030902003195號

粵公網安備 44030902003195號