近日,中國科大國家示范性微電子學院程林教授課題組設計的兩款電源管理芯片(高效率低EMI隔離電源芯片和快速大轉換比DC-DC轉換器芯片)亮相集成電路設計領域最高級別會議 IEEE International Solid-State Circuits Conference (ISSCC)。ISSCC是國際上最尖端芯片技術發表之地,其在學術界和產業界受到極大關注,也被稱為 “芯片奧林匹克”。ISSCC2022于今年2月20日至28日在線上舉行。

高效率低EMI隔離電源芯片

隨著隔離電源的尺寸越來越小,芯片內部功率振蕩信號頻率和功率密度也越來越高。隔離DC-DC轉換器往往會成為輻射源,導致電磁干擾(EMI)問題。傳統隔離DC-DC轉換器降低EMI的方法大多局限于板級層面,開發成本高且無法從根源上解決EMI輻射問題。本研究提出了一種對稱型D類振蕩器的發射端拓撲結構,在芯片層面上減小隔離電源系統的共模電流以降低EMI輻射。同時,該研究提出的死區控制方法可以巧妙避免從電源到地的瞬時短路電流。此外,該研究提出的架構只采用了低壓功率管,從而有效提高了振蕩器的轉換效率,降低了芯片成本。

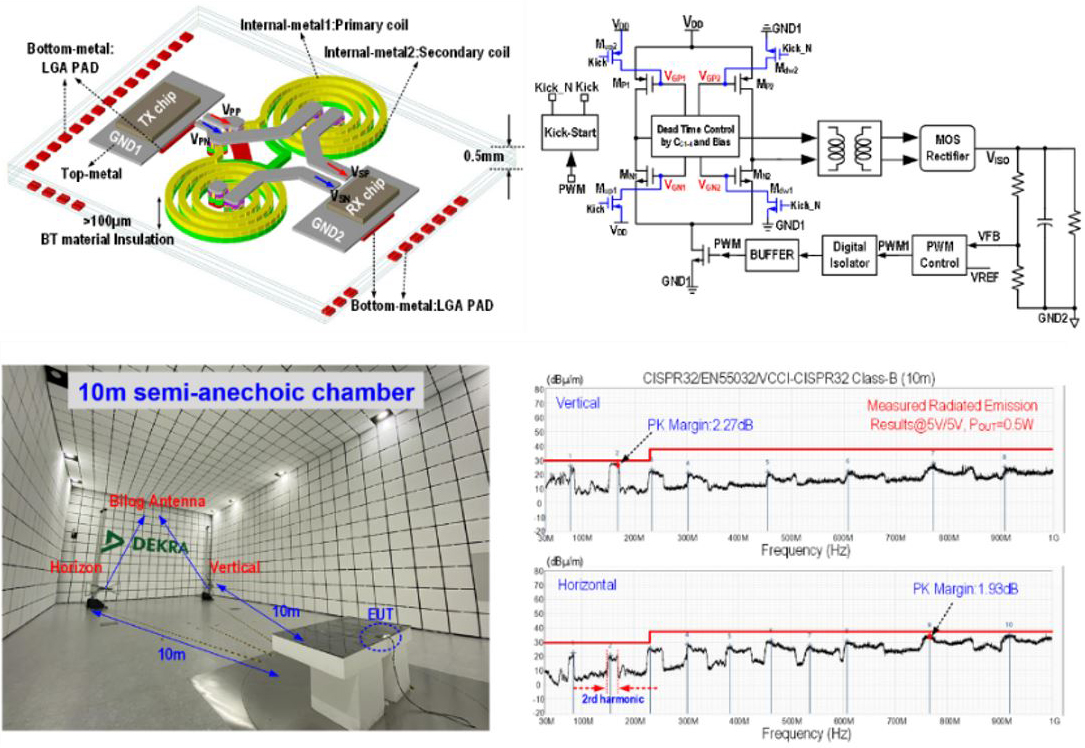

圖1. 隔離電源芯片電路結構與EMI測試結果

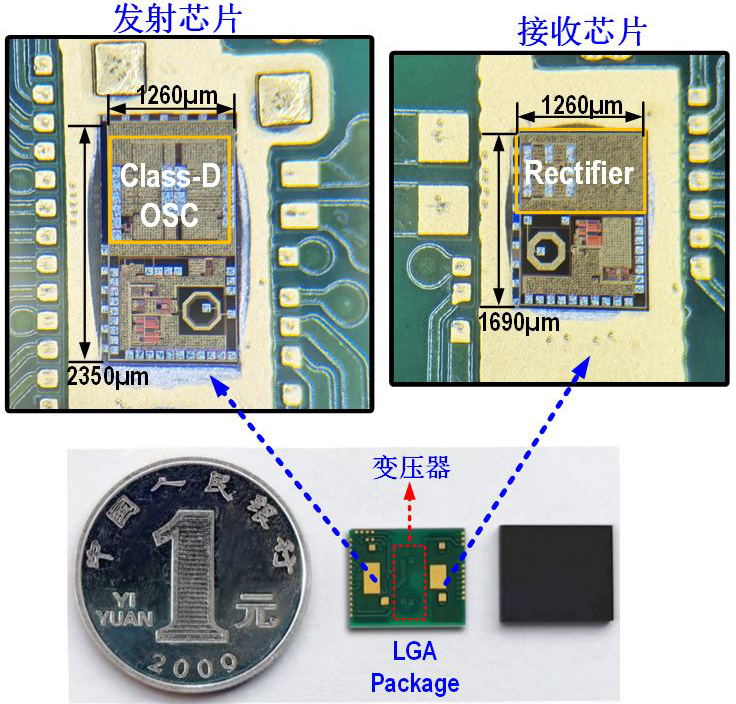

最終測試結果表明該芯片實現了51%的峰值轉換效率和最大1.2W的輸出功率,并且在專業的10米場暗室中實測通過了CISPR-32的B類EMI輻射國際標準,研究成果以“A 1.2W 51%-Peak-Efficiency Isolated DC-DC Converterwith a Cross-Coupled Shoot-Through-Free Class-DOscillator Meeting the CISPR-32 Class-B EMI Standard”為題發表在ISSCC2022上。第一作者為我校微電子學院特任副研究員潘東方,程林教授為通訊作者,蘇州納芯微電子為論文合作單位。這是課題組連續第二年在隔離電源芯片設計領域發表的ISSCC論文。

圖2. 隔離電源芯片和封裝照片

快速大轉換比DC-DC轉換器芯片

單級大轉換比DC-DC轉換器因其具備低傳輸線損耗、綜合效率高等優勢,在數據中心、5G通信基站等領域具有廣闊的應用前景。現有的大轉換比DC-DC轉換器多采用多相DC-DC轉換器與串聯電容相結合的混合拓撲結構,以實現等效轉換比的擴展,但其負載瞬態響應速度受多相間固定相位差以及多相結構無法同時導通的限制。

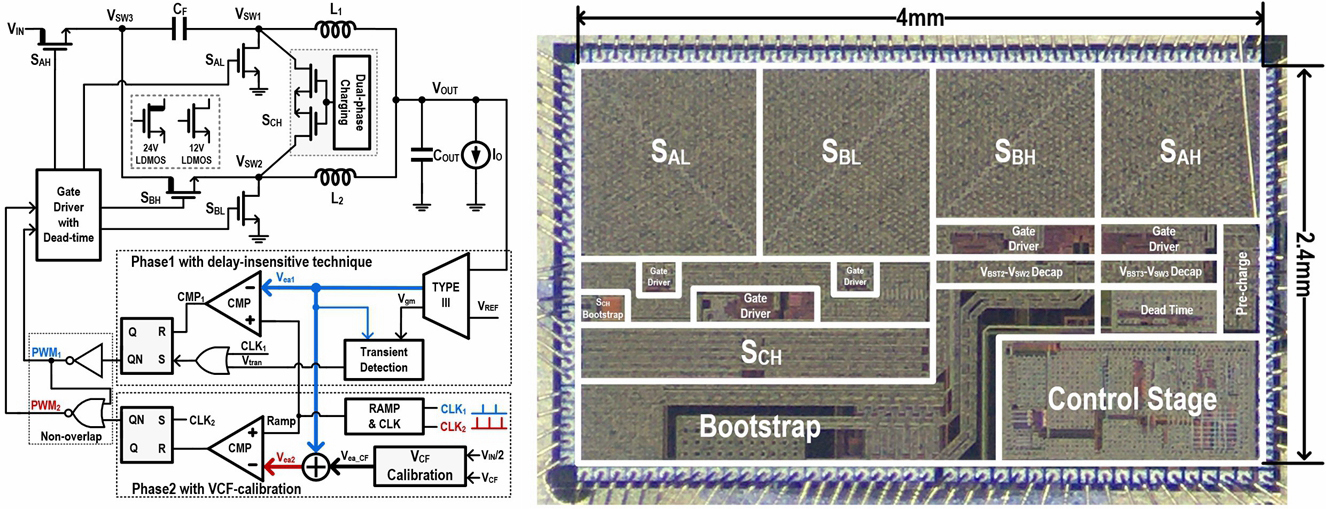

圖3. 快速大轉換比DC-DC轉換器電路結構與芯片照片

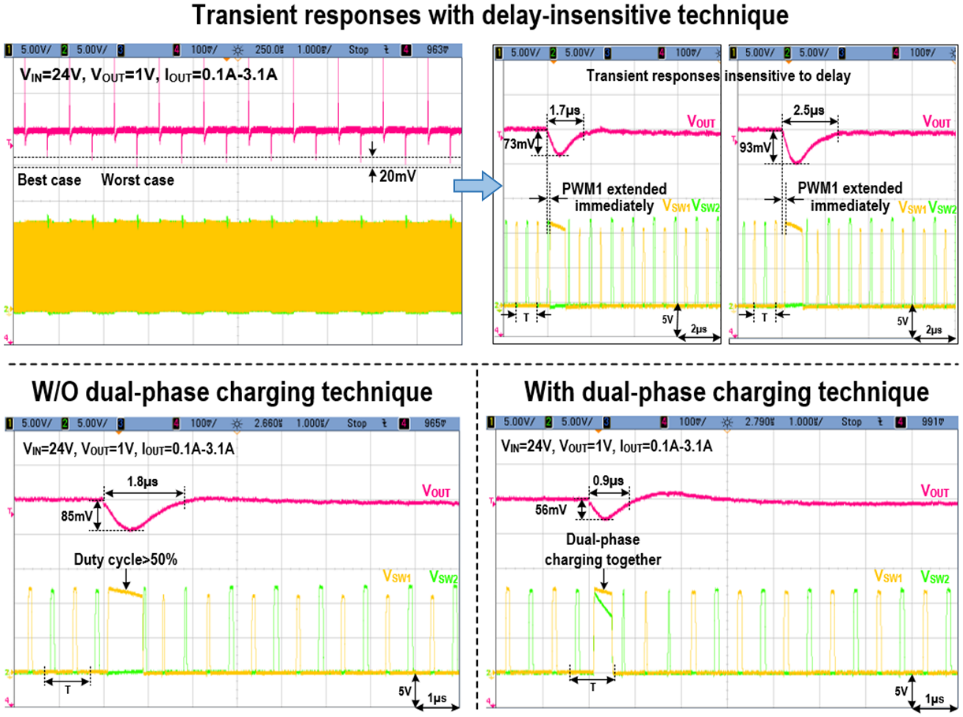

本研究基于兩相串聯電容式DC-DC轉換器拓撲結構,提出了雙反饋環路的電壓模式PWM控制方法,實現對輸出電壓和串聯電容電壓的調制。同時,本研究還提出了快速瞬態響應技術,既克服傳統PWM控制方法存在的環路響應速度與負載跳變時刻有關的缺點,也可以利用兩相電感電流同步對負載充電以進一步提高轉換器的響應速度。最終測試結果表明本研究在3A電流的負載跳變下實現了僅0.9µs的恢復時間,取得了目前同類研究中最快的負載瞬態響應速度,研究成果以“A 12V/24V-to-1V DSD Power Converter with56mV Droop and 0.9µs 1% Settling Timefor a 3A/20ns Load Transient”為題發表在ISSCC2022上。第一作者為我校微電子學院博士生苑競藝,程林教授為通訊作者。

圖4. DC-DC轉換器芯片負載瞬態測試結果

上述兩項研究得到了國家自然科學基金委、科技部和中科院等項目的資助。

ISSCC會議官網:https://www.isscc.org/

粵公網安備 44030902003195號

粵公網安備 44030902003195號