作者:泰克科技中國AE Manager,余洋

高速總線升級迭代的矛盾在于,消費者對性能的需求驅動著信號速率成倍的增長,消費者對便捷性的需求使得傳輸線無法縮短,消費者對低成本的追求要求PCB板材和傳輸線不能太貴,這就導致ISI抖動變得越來越嚴重。均衡(Equalization)就是為了應對ISI抖動,而被廣泛應用的黑科技。既然ISI抖動的根源,是傳輸鏈路對不同頻率信號損耗的差異,均衡就是要想辦法補償掉這個差異,讓不同頻率信號的幅度都能保持均勻。

根據均衡技術所使用的位置,一般分為發送端均衡(Tx EQ)和接收端均衡(Rx EQ)。

發送端均衡一般采用前向均衡(FFE, Feed Forward Equalization) 技術,用一組移位寄存器配合乘法器和加法器,根據當前bit位r(n)受到前若干bits r(n-1) 、r(n-2) 、r(n-3)…的影響,來修正r(n)的電壓值。典型的表達式是:

e(n)=r(n)*k1+r(n-1)*k2+…

這個表達式有N項,就稱之為N階FFE,代表當前bit的電平,受到自身及前(N-1) bits的影響。在高速串行中應用最廣泛的“預加重/去加重“(Pre/De-emphasis)技術,就是一個二階的FFE,它會根據當前bit和前1 bit的邏輯狀態,來調整當前bit的電平。

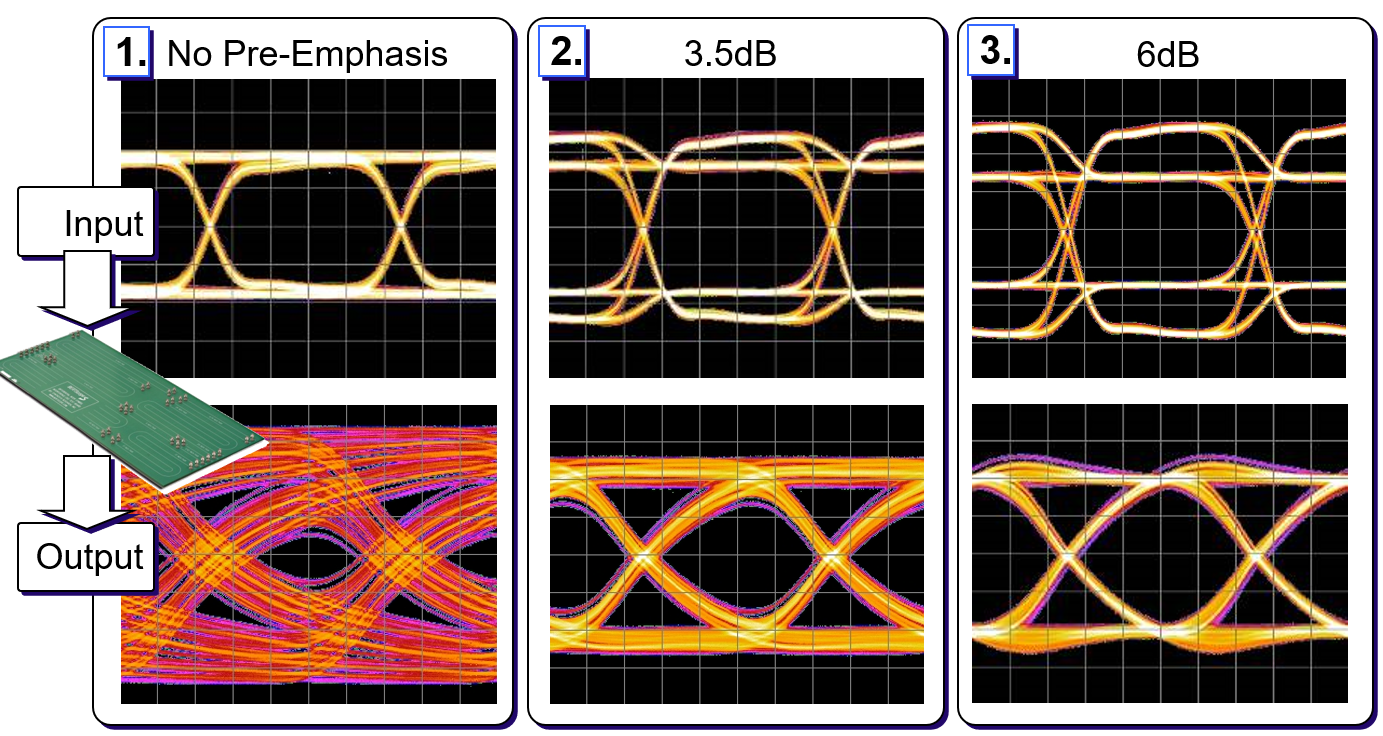

我們來看一個Pre-emphasis的真實案例。當發送端的信號不做任何處理時,發送端眼圖是很完美的;一旦信號經過長背板傳輸之后,嚴重的ISI抖動會導致眼圖幾乎閉合(例1)。當發送端增加3.5dB預加重時,會將頻率較高的跳變沿信號(Transition Bits,指的是與前一bit邏輯狀態不同的bit,如01碼型中的1,或110碼型中的0等) 的幅度增強3.5dB。這些預先的增強會部分抵消長背板的損耗,從而不同碼型的電平在到達接收端時基本相等,ISI抖動就大幅降低了。接收端的眼圖無論是眼高眼寬,還是抖動,都有非常明顯的改善(例2)。

圖20:發送端均衡對眼圖的影響

如果說發送端均衡是未雨綢繆,那么接收端均衡就是亡羊補牢。當ISI 抖動已經傳遞到了接收端,接收端應該如何進行均衡,嘗試得到更好的眼圖呢?接收端均衡一般采用CTLE(連續時間線性均衡)或DFE(負反饋均衡),或二者結合的方式,來降低數據的ISI抖動。

DFE均衡和FFE類似,不同的是DFE有負反饋調節功能。通過負反饋,可以自適應均衡系數,以達到最佳的均衡效果。同時, DFE不僅能消除ISI抖動,對于通道間的串擾也能提供一定的補償效果,對于信號完整性的提升用處很大。

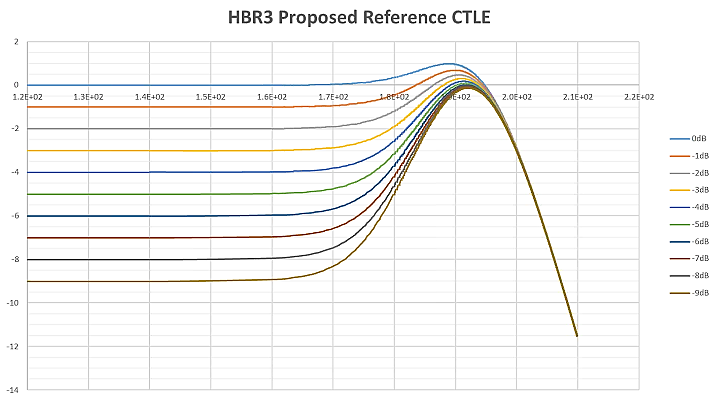

CTLE 的實現方法和FIR濾波器有點像,實現的是一個近似帶通濾波器的效果。下圖是一組典型的CTLE濾波器,低頻衰減大,而高頻衰減小。這個濾波曲線,和傳輸鏈路的損耗正好形成互補(傳輸鏈路插入損耗是低頻衰減小,而高頻衰減大)。在接收端,實現了不同頻率間均勻的總體損耗,從而降低了ISI抖動。CTLE和DFE/FFE不同,它不依賴參考時鐘,在連續時間域上對信號進行均衡;而DFE/FFE是數字域上的均衡,必須要先有參考時鐘,來區分不同的bit,才能進行均衡。接收端常常使用CTLE和DFE的組合,先用CTLE打開近乎閉合的眼圖,恢復出時鐘,再用DFE進一步均衡補償。

圖21:典型的CTLE均衡類似于帶通濾波器

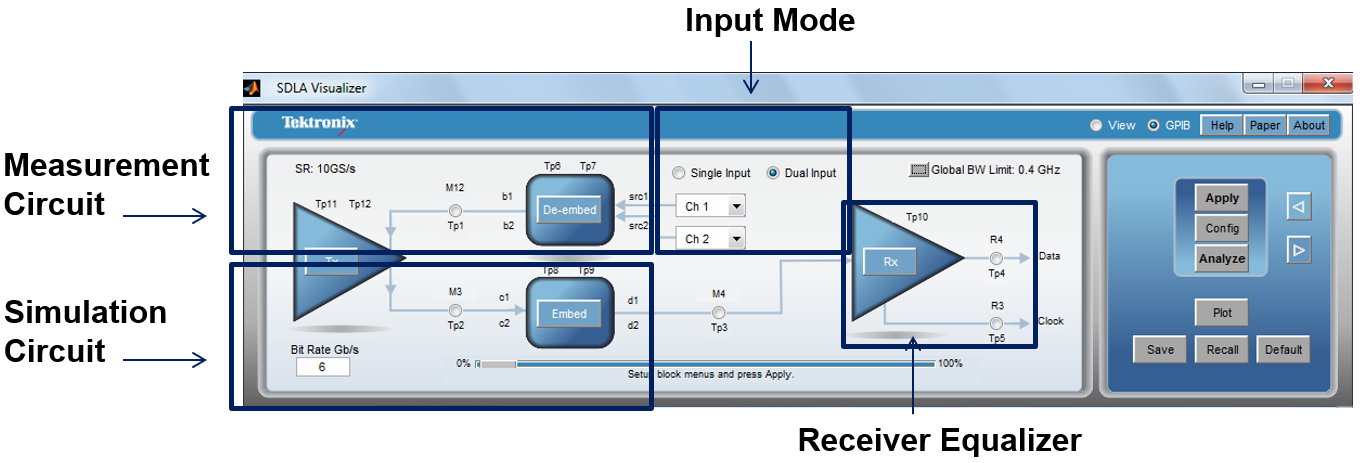

設計工程師為了解決ISI問題,常常需要在鏈路損耗和均衡技術之間做出綜合考慮。泰克的SDLA軟件可以模擬發送端的Tx EQ和接收端的Rx EQ,還能模擬傳輸鏈路的不同損耗。

圖22:SDLA軟件支持發送端、接收端均衡,以及鏈路嵌入/去嵌模擬

讓你在產品設計的初期,就能預估鏈路的ISI抖動,探索和嘗試最佳的均衡組合以降低ISI抖動,大幅減少產品研發的時間。

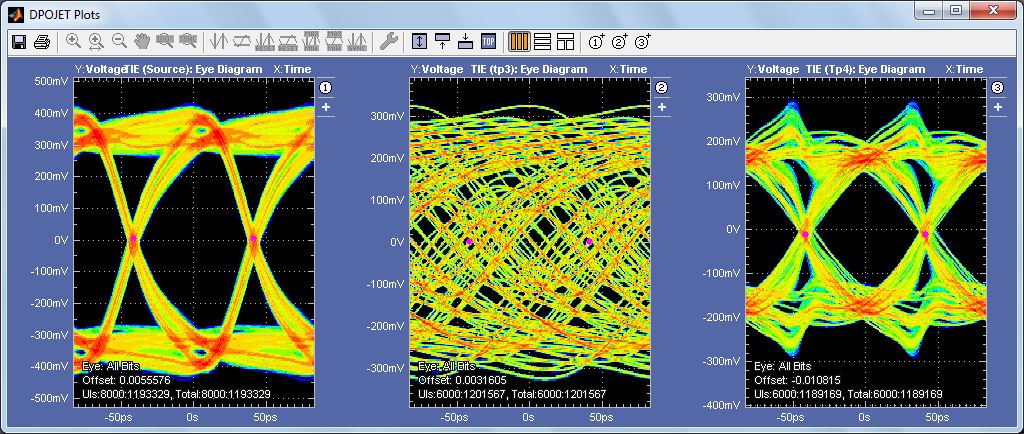

圖23:發送端眼圖,通過SDLA通道嵌入得到的接收端眼圖,通過SDLA接收機均衡得到的最終眼圖

了解泰克高速串行通信更多解決方案,https://www.tek.com.cn/solutions/application/high-speed-serial-communication。

關于泰克科技

泰克公司總部位于美國俄勒岡州畢佛頓市,致力提供創新、精確、操作簡便的測試、測量和監測解決方案,解決各種問題,釋放洞察力,推動創新能力。70多年來,泰克一直走在數字時代前沿。歡迎加入我們的創新之旅,敬請登錄:tek.com.cn

粵公網安備 44030902003195號

粵公網安備 44030902003195號