作者:Gweneivere Lasay,產品應用工程師

摘要

假晶高電子遷移率晶體管(pHEMT)是耗盡型器件,其漏源通道的電阻接近0 Ω。此特性使得這些器件可以在高開關頻率下以高增益運行。然而,如果柵極和漏極偏置時序不正確,漏極溝道的高電導率可能會導致器件燒毀。本文探討耗盡型pHEMT射頻(RF)放大器的工作原理以及如何對其有效偏置。耗盡型場效應晶體管(FET)需要負柵極電壓,并且必須小心控制開啟/關斷的時序。文中將介紹并比較固定柵極電壓和固定漏極電流電路。我們還將仔細研究這些偏置電路的噪聲和雜散對RF性能有何影響。

引言

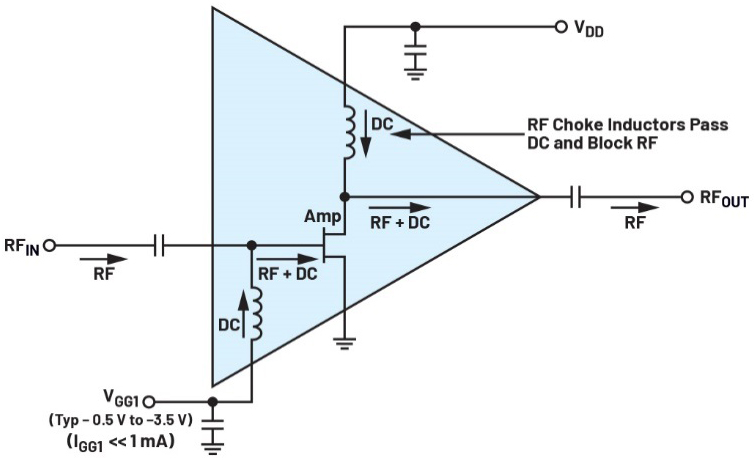

圖1顯示了耗盡型pHEMPT RF放大器的簡化框圖。流經器件的RF信號路徑是從柵極到漏極,交流耦合電容將RF信號與漏極和柵極上的直流偏置電壓去耦。主電源電壓通過電感施加到FET晶體管的漏極。

圖1.耗盡型RF放大器的簡化架構。

耗盡型器件的一個重要特性是,當柵極電壓等于0 V時,漏源電阻接近0 Ω。因此,要操作這種器件,必須對柵極施加負電壓。在圖1中,該電壓通過片上電感施加。

這種偏置方法的一個缺點是,兩個電源不能同時開啟。在柵極偏置電壓之前施加漏極偏置電壓會導致漏極電流突然增加,從而很快燒毀器件。因此,必須首先施加負柵極偏置電壓來夾斷溝道。開啟和關閉放大器時,應使用表1中的步驟。

表1.放大器步驟

|

上電序列 |

關斷序列 |

|

1.向柵極施加負電壓以將柵極置于夾斷模式。 |

1.去除RF信號。 |

|

2.向漏極施加正電壓。 |

2.降低柵極電壓(負電壓更大)以夾斷柵極。 |

|

3.增加柵極電壓以實現靜態電流。 |

3.將漏極電壓減小至0 V。 |

|

4.施加RF信號。 |

4.將柵極電壓增加至0 V。 |

實踐中可以跳過夾斷步驟。例如,如果知道正常工作的最終柵極電壓,那么可以立即施加該電壓,而無需經過夾斷步驟。

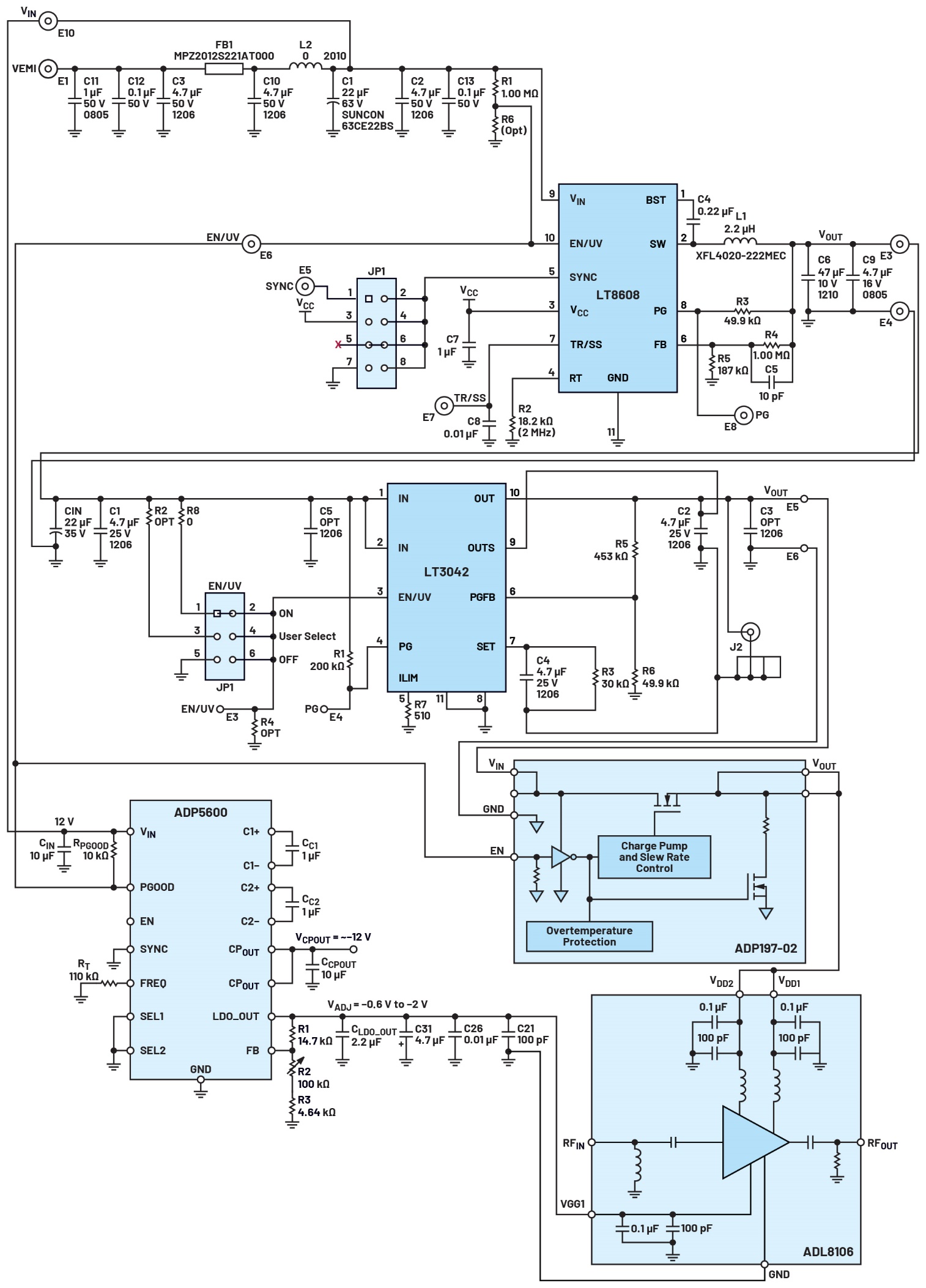

固定柵極電壓偏置

圖2顯示了耗盡型RF放大器建立并維持固定柵極電壓的電源管理電路。它使用開關穩壓器、低壓差(LDO)穩壓器和負載開關來產生漏極電壓。柵極電壓由ADP5600產生,該器件包含電壓逆變器和LDO穩壓器。漏極電流由負電壓LDO穩壓器的反饋電阻設置。為確保安全的電源時序,開關穩壓器的使能(EN)引腳與負電壓發生器的電源良好(PGOOD)信號相連。這確保了負柵極電壓始終出現在漏極電壓之前。

圖2.固定柵極電壓偏置。

圖3.固定漏極電流偏置(有源偏置控制)

此電路的主要缺點是沒有考慮RF放大器VGATE與IDRAIN關系的器件間差異。漏極電流的器件間差異(假設柵極電壓固定)可能很大,導致每個電路具有不同的漏極電流。漏極電流差異通常會影響壓縮(OP1dB)和三階交調失真(OIP3)(增益也會受到影響,但程度較小)。這種方法的好處之一是漏極電流將根據RF輸入功率和RF輸出功率的變化而增加或減少。因此,如果RF輸入功率較低,功耗也會較低,反之亦然。

有源偏置控制

有源偏置控制是另一種方法。此技術不是固定柵極電壓,而是固定漏極電流。圖3中,有源偏置控制器通過測量漏極電流并改變柵極電壓來調節漏極電流,使該電流即使在不同的RF輸入條件下也能保持固定。此電路由LT8608降壓穩壓器和HMC920有源偏置控制器組成,后者可支持3 V至15 V的漏極電壓和高達500 mA的總漏極電流。

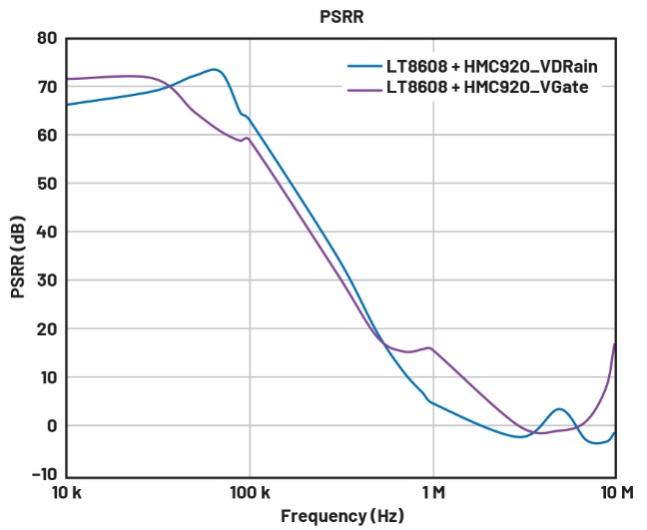

HMC920內部的高電壓、高電流線性穩壓器(LDOCC引腳)可產生3 V至15 V的正電壓和高達500 mA的電流。其輸出通過內部MOSFET開關連接至VDRAIN端口,用于控制電源時序。為了設置功率放大器所需的漏極電壓,必須使用公式1調整LDO穩壓器的反饋電阻R5和R8:

其中,VDRAIN是所需的漏極電壓值,IDRAIN是所需的漏極電流。常數0.5是內部MOSFET開關的RDS(ON)值。

內部電荷泵產生負電壓VGATE。通過讀取RSENSE處的電壓,控制器檢測漏極電流并改變VGATE處的電壓。要設置漏極電流,必須使用公式2改變RSENSE(R4和R19):

當通過施加電源電壓(VDD)開啟HMC920時,會有一個信號發送至EN引腳以啟動控制環路。VDRAIN最初會短接到地,以強制將其設為零。同時,VGATE處的電壓最初會被拉低至最小電壓VNEG。然后,VDRAIN將提高至設定的漏極電壓值。RSENSE上將產生電壓降,這會導致控制器改變柵極電壓。關斷期間,會有一個邏輯低電平信號發送至EN引腳。VGATE將降低至VNEG以切斷放大器,VDRAIN處的電壓將降至零。VGATE處的電壓最終將達到零。此周期遵循正確的電源時序,以確保耗盡型放大器安全運行。它還具有過流和欠流報警、短路保護、功率折返等安全特性。HMC920數據手冊中詳細解釋了該偏置控制器的其他安全機制。

該偏置控制器用作ADL8106寬帶低噪聲放大器的電源管理解決方案。ADL8106的工作頻率范圍為20 GHz至54 GHz,標稱漏極電壓為3 V,靜態漏極電流為120 mA。圖4和圖5顯示了相關的開啟和關斷波形。

圖4.開啟時的電源時序波形。一旦施加VDD,EN變為高電平就表示控制環路啟動。首先開啟VGATE,然后開啟VDRAIN。

圖5.關斷時的電源時序波形。當VDD被移除時,EN變為低電平。VGATE將再次降至最小電壓VNEG,VDRAIN將降至零。然后,VGATE最終將達到零。

噪聲和雜散抑制

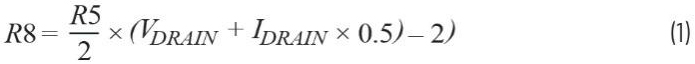

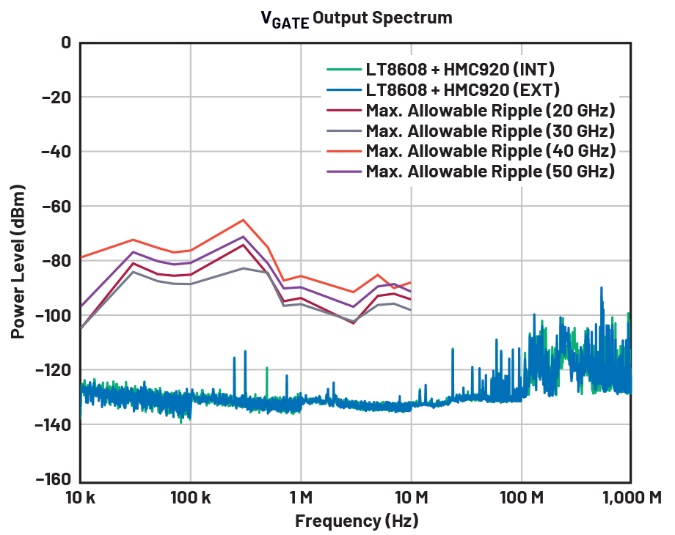

RF放大器RF輸出端的雜散和噪聲水平將取決于HMC920的輸出噪聲和雜散,以及放大器的電源調制比(PSMR)。圖6顯示了開關穩壓器(LT8608)輸入端以及VDRAIN和V_GATE輸出端口的PSRR曲線。圖7和圖8顯示了VGATE和VDRAIN電壓的輸出頻譜。基于ADL8106的PSMR,這些圖中還包含了顯示最大允許輸出噪聲和雜散的跡線。電源管理電路的輸出噪聲和雜散必須低于這些水平,以確保放大器的性能不會因電源管理電路而降低。有關該參數的理論、測量和計算的更深入解釋,請參閱優化信號鏈的電源系統系列文章。

圖6.LT8608 + HMC920的電源電壓抑制比(VDD = 5 V,VDRAIN = 3 V,IDQ = 120 mA,VGATE = –0.64 V)。

圖7.HMC920的V GATE和V DRAIN輸出頻譜以及ADL8106的最大允許噪聲限值。

圖8.HMC920的V GATE和VDRAIN輸出頻譜以及ADL8106的最大允許噪聲限值。

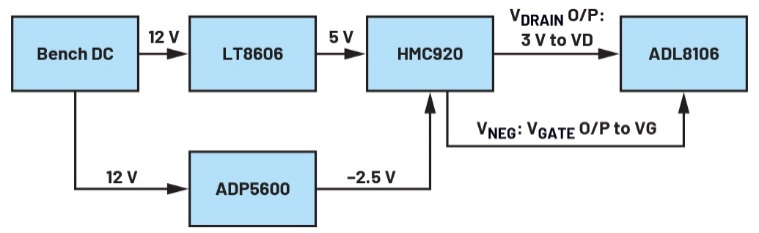

使用外部負電源操作HMC920

在前面的示例中,HMC920的內部負電壓發生器用于生成負柵極電壓。此外也可以使用外部負電源,如圖9所示。在這種情況下,ADP5600(逆變器和負LDO穩壓器)用作產生柵極電壓的負電源。與使用內部負電壓發生器相比,其結果是噪聲系數略低且增益略高。

圖9.外部VNEG模式下的ADL8106和HMC920框圖。

圖10.使用HMC920的ADL8106在內部負電壓發生器模式和外部負電壓發生器模式下的噪聲系數。

圖11.使用HMC920的ADL8106在內部負電壓發生器模式和外部負電壓發生器模式下的增益。

該模式下的實際噪聲性能仍然取決于所用外部負電壓發生器所產生的輸出噪聲。從圖7和圖8中可以看出,在外部VNEG模式下使用HMC920也會產生噪聲雜散,這些雜散仍低于最大允許電壓紋波限值。要利用此模式,必須將VNEGFB引腳短接至地以禁用負電壓發生器的反饋控制。對于增強型放大器(正柵極電壓),VNEGFB和VGATEFB引腳都必須接地。

結語

耗盡型GaAs放大器因其寬帶寬和高動態范圍而廣泛用于RF應用。但是,此類放大器需要負偏置電壓,并且必須小心控制其電源時序。可以使用固定的負柵極電壓來偏置這種放大器。其好處是電流消耗是動態的,隨著RF輸出電平而變化。本文介紹的電路使用固定漏極電流,產生低噪聲漏極和柵極電壓并安全控制其時序,這些電壓不會降低RF放大器的額定性能。這樣器件間的性能差異會更小,因為每個器件都以相同的漏極電流運行。然而,這種方法的一個缺點是漏極電流是固定的,不隨RF功率水平而變化。在決定固定漏極電流水平時應謹慎考慮,它必須足夠高才能支持所需的最大輸出功率水平,但又不能過高以至于導致電流浪費。雖然可以使用外部負電源代替HMC920的內部負電壓發生器,但對噪聲的改善作用微乎其微。

關于ADI公司

Analog Devices, Inc. (NASDAQ: ADI)是全球領先的半導體公司,致力于在現實世界與數字世界之間架起橋梁,以實現智能邊緣領域的突破性創新。ADI提供結合模擬、數字和軟件技術的解決方案,推動數字化工廠、汽車和數字醫療等領域的持續發展,應對氣候變化挑戰,并建立人與世界萬物的可靠互聯。ADI公司2022財年收入超過120億美元,全球員工2.4萬余人。攜手全球12.5萬家客戶,ADI助力創新者不斷超越一切可能。更多信息,請訪問www.analog.com/cn。

關于作者

Gweneivere Lasay 2017年畢業于馬普阿大學,獲電子工程學士學位。她在功率半導體和SMPS設計領域擁有4年多的專業經驗。她于2022年3月加入ADI公司,擔任射頻和高速電源連接部門的產品應用工程師。

粵公網安備 44030902003195號

粵公網安備 44030902003195號