作者:Erik Lamp,產品應用工程師和Xinyu Liang,應用工程經理

摘要

本文提供一種多相單片式降壓解決方案,旨在應對構建處理單元的電源時需滿足的大電流、快速瞬態響應要求。我們采用稱之為Silent Switcher® 3架構的新型低輸出噪聲技術,其快速瞬態響應特性支持多相操作。該解決方案具有出色的高控制帶寬,使用的輸出電容比其他方案更少,有助于電源在瞬態期間更快速地恢復。本文詳細介紹設計技巧和考慮因素,以幫助工程師優化未來的設計。

簡介

在當今的計算環境中,CPU、FPGA和ASIC的功耗日益增加。對于5G收發器、波束成形器和其他高速RF等一些更具體的應用,考慮帶寬和RF噪聲水平時,功率要求甚至更加嚴格。傳統的雙極(降壓+LDO)解決方案廣泛用于RF應用中,由于輸出電流高,不僅體積大、效率低,還需要更高水平的散熱。隨著對輸出電流能力的要求不斷提高,使用單個降壓穩壓器為高需求負載供電變得不劃算。而多相降壓穩壓器因可擴展性和紋波交錯優勢,電流傳輸性能出色,因此被廣泛用于該領域。但是,要達到快速瞬態響應和超低RF噪聲要求,多相降壓穩壓器需要采用多個輸出電容和多級LC濾波器來為高速RF ASIC供電。這些額外的組件通常會占用很大一部分板空間,并且還可能增加解決方案的成本。本文展示使用高性能Silent Switcher 3架構所具有的優勢,在多相降壓應用中,該架構可提供超低噪聲和快速瞬態響應。本文還介紹針對不同的ASIC負載要求,如何通過不同的設計考慮因素來解決。

Silent Switcher 3架構采用超低噪聲設計(在10 Hz至100 kHz范圍內一般為4 μV rms),包含高增益誤差放大器,提供超低EMI輻射和快速瞬態響應。在該新產品系列中,LT8627SP具有最高16A額定電流,因此非常適合用于大電流、噪聲敏感型應用中的多相降壓配置。由于所有ASIC負載具有低電源電壓特性(<1V)并且廣泛使用12V配電系統,因此多相降壓穩壓器對最短導通時間非常敏感。Silent Switcher 3技術采用創新架構,提供非常短的導通時間(15 ns),使LT8627SP在1 MHz以上的開關頻率下也能輕松運行,有助于改善紋波、尺寸、噪聲和帶寬。

針對50A電流RF數字負載,盡可能縮短瞬態恢復時間

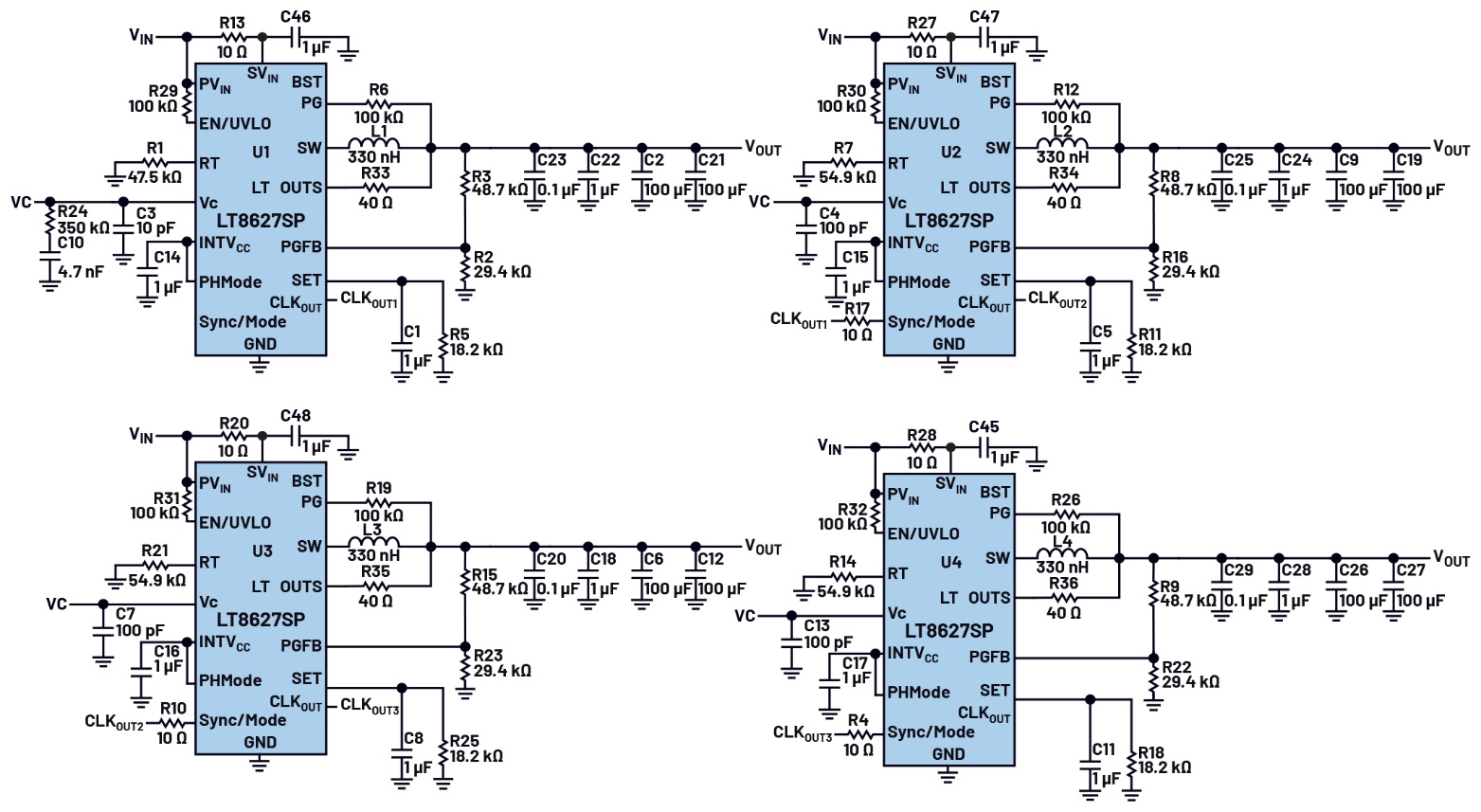

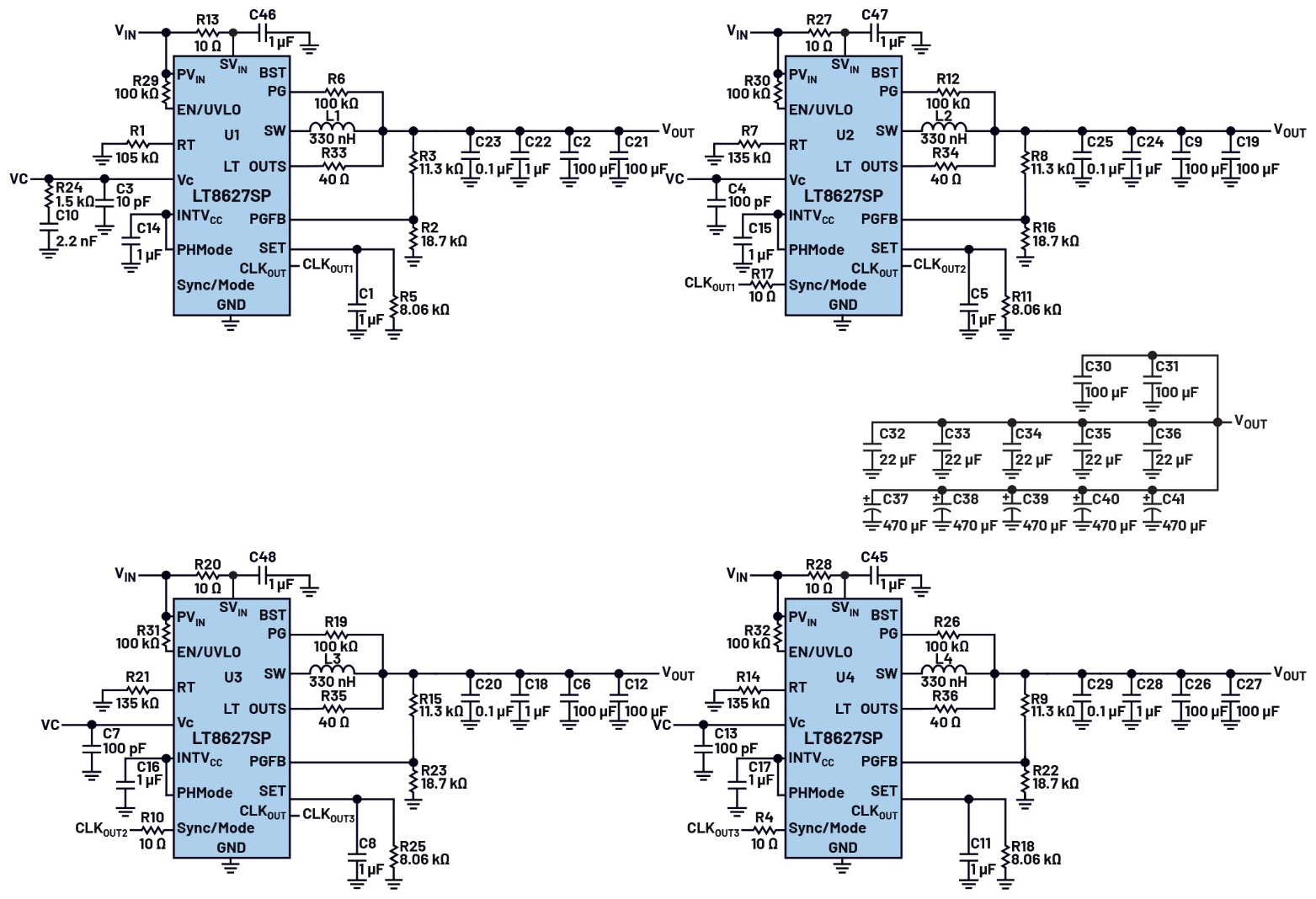

決定電源性能的一個重要特性是其恢復時間。這是在發生負載瞬態時,輸出電壓恢復到穩壓值所需的時間。每個電源的恢復速度都有限制,與控制環路帶寬相關。控制環路帶寬更高,意味著電感電流在瞬態期間能夠更快地爬升/回落,以補償輸出電容的電荷變化,在更快時間內完成恢復過程。圖1展示了一個使用四相LT8627SP的示例:為1.8 VOUT RF數字負載供電,最大負載電流為50A。該電源設計為在2 MHz開關頻率下輸出1.8 V電壓。為了縮短瞬態期間的電荷補償時間,該設計中使用低ESR陶瓷電容,并且避免使用高ESR聚合物電容和電解電容。采用交錯PWM技術(每相90°)來增加等效紋波頻率,從而增大控制帶寬。

圖1.為1.8 VOUT、50 A RF數字負載供電的四相交錯LT8627SP解決方案。

對補償網絡進行調節,以實現至少45°相位裕量和大于8 dB的增益裕量,同時盡可能增大帶寬。因此,在45°相位裕量和9 dB增益裕量下,其控制環路調諧到最大280 kHz的帶寬,如圖2中的波特圖所示。為了進行比較,我們在1.8 V、12 A輸出下,對具有等效單相輸出電容(2 × 100 µF + 1 × 1 µF + 1 × 0.1 µF)的單相LT8627SP進行了測試。采用相同穩定性標準的伯德圖如圖2所示。

圖2.50A/四相LT8627SP和12A/單相LT8627SP的伯德圖比較。

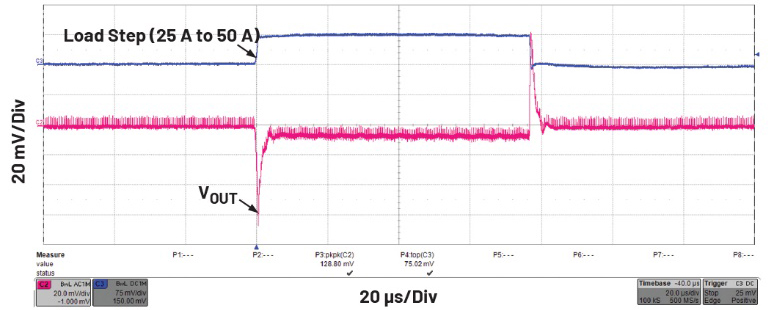

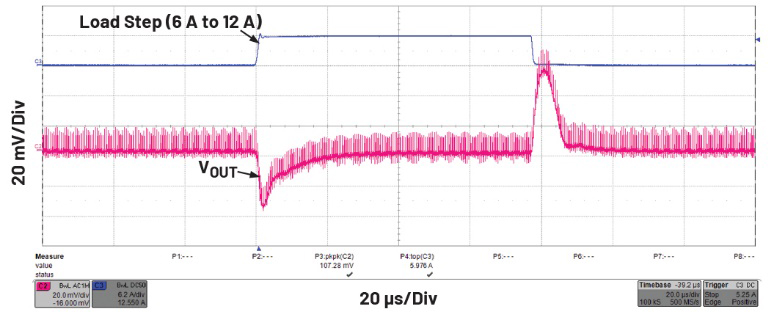

為了通過測試比較恢復時間,四相和單相LT8627SP均采用50%負載瞬態,采用每相6A/µs擺率。測試結果如圖3所示,瞬態上升沿的恢復時間約為2.5 μs。與圖4中的單相LT8627SP相比,恢復時間將近縮短10倍。

圖3.四相LT8627SP 25 A至50 A負載瞬態優化,以實現最短恢復時間。

圖4.單相LT8627SP 6 A至12 A負載瞬態優化,以實現最短恢復時間。

針對大電流無線應用,盡可能減少瞬態VPP

Silent Switcher 3架構的多相操作已用于許多客戶的電源設計。圖5展示了另一個示例:LT8627SP如何幫助無線客戶在0.8 VOUT和22 A至60 A 1 µs負載瞬態下,為快速、大電流瞬態SoC供電。為防SoC性能因瞬態降低,需要VPP小于5% (40 mV)。

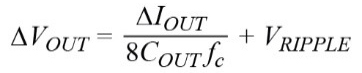

如前文所述,我們已知四相交錯LT8627SP可以提供很高的控制帶寬,約在300 kHz左右。而在時域內,我們可以大致模擬負載瞬態期間的電壓變化與控制帶寬之間的關系,如下所示:

由此可以得出,在紋波電壓為10 mV時,最小輸出電容為1583 µF。在設計中,所選的電容應大于該值,不同于之前所述,需使用更多聚合物電容,以在瞬態期間提供足夠的阻尼。我們需通過不斷試驗和試錯來確定最終的輸出電容,因為它也會影響環路帶寬和穩定性。

圖5.四相交錯LT8627SP解決方案,在0.8 V、22 A至50 A 1 µs瞬態下實現<5% VPP。

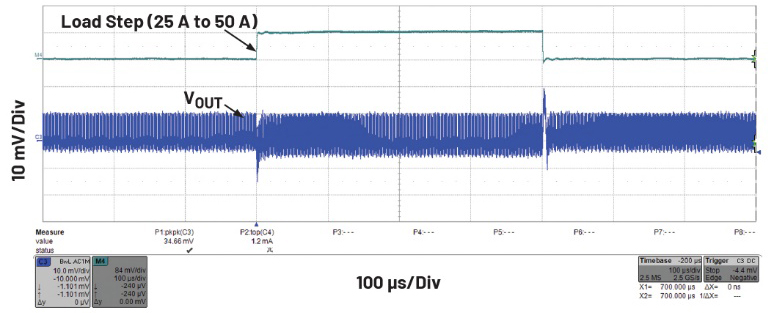

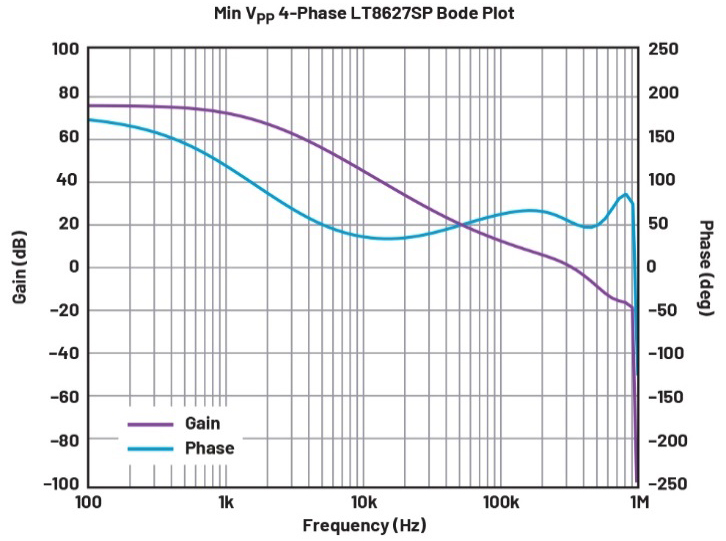

四相LT8627SP在1 MHz開關頻率下交錯,匯聚合成為4 MHz紋波頻率。在確定最小輸出電容之后,在22 A至50 A瞬態負載、28 A/µs擺率下,實現35 mV (4.4%) VPP。瞬態波形如圖6所示。為了驗證控制環路的穩定性,使用50 A負載,進行波特圖測量。結果如圖7所示。在50 A時,控制環路的帶寬為322 kHz,具有50°相位裕量。

圖6.在28 A/µs擺率下,22 A至50 A負載階躍的瞬態波形。

圖7.四相最小VPP值解決方案的伯德圖。

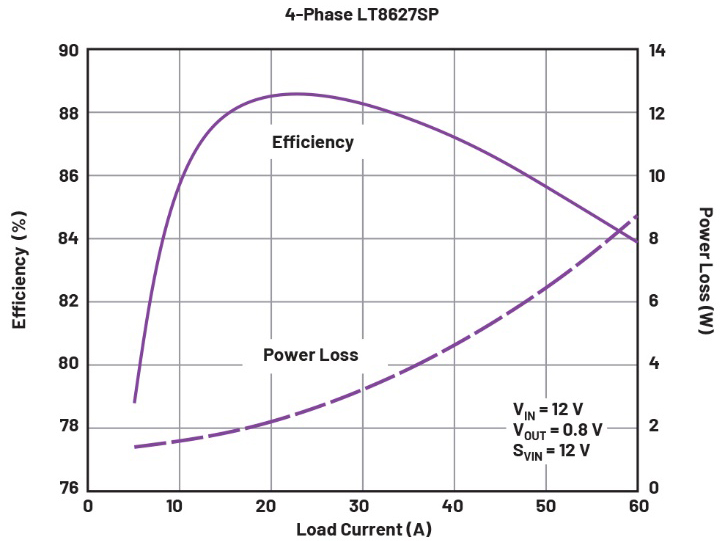

為了進行更多性能測試,我們測量了效率和滿負載熱性能。測試了12 VIN、0.8 VOUT、最高60 A負載下的效率,如圖8所示。包含輔助損耗在內,轉換器在25 A負載下的峰值效率為89%,在60 A負載下的效率為84%。

圖8.四相交錯LT8627SP在1 MHz FSW、12 VIN和0.8 VOUT下的效率。

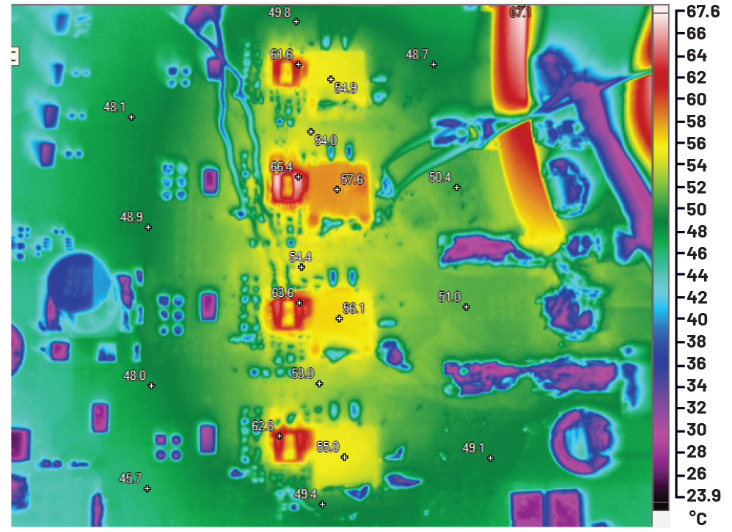

圖9以熱圖方式顯示了這個四相設計的熱性能。在60 A負載下,IC最高溫度為66°C,最低溫度為61.6°C。四個IC之間的最大溫差為5°C左右,表示各相均流性能出色。

圖9.四相交錯LT8627SP在1 MHz FSW、12 VIN和0.8 VOUT 60 A下的熱性能。

關于多相LT8627SP的設計考慮因素和指南

LT8627SP作為峰值電流模式控制IC,可輕松配置為多相操作。有幾項設計考慮因素需特別注意,分別是:

? 要實現正常均流,需將每個IC的VC引腳連接在一起,如圖1的原理圖所示。

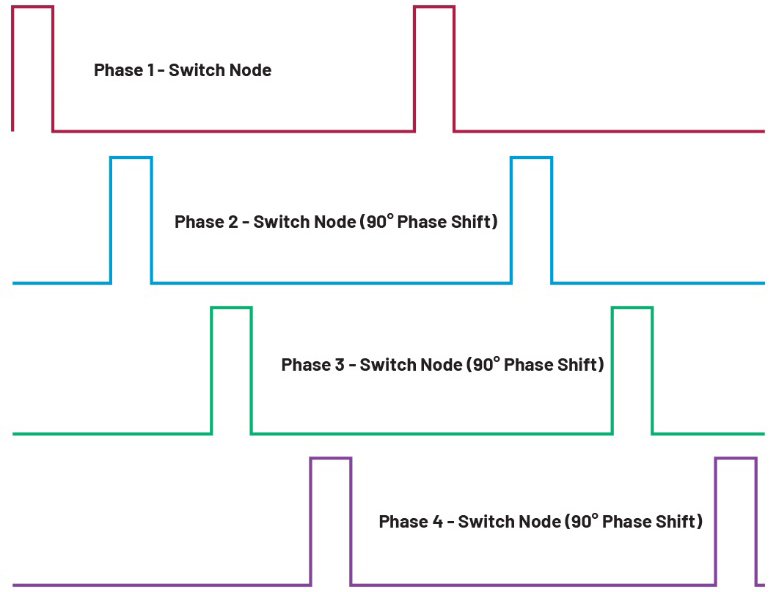

? 要以均衡的方式交錯連接四相LT8627SP,每個IC的CLKOUT需配置為90°相移,并饋入下一個IC的SYNC引腳。采用該配置時,每個IC的開關節點波形如圖10所示。交錯是多相降壓穩壓器帶來的最大優勢之一。均衡交錯的相位能夠使輸出電壓紋波頻率倍增,因此可顯著降低輸出電容。交錯紋波頻率更高時,也有助于控制環路有效抑制更高帶寬下的紋波噪聲。LT8627SP可以采用高達4 MHz開關頻率,支持三種不同的相移時鐘配置:180°、120°和90°。這表示無需額外使用任何器件,也能實現最多12種交錯。

? 為了實現正常的電壓檢測,應將每個IC的OUTS引腳連接在一起。需要注意的是,因為控制環路中涉及到所有誤差放大器(EA),在進行伯德圖導入時也需要考慮所有EA。因此,需要將檢測點(輸出電壓)和OUTS引腳側連接在一起,確保每個EA都能實現均勻擾動。

? RT引腳需使用電阻來設置頻率。主機IC需提供設置目標開關頻率所需的電阻值,從機IC的電阻值設置的頻率要比主機IC低20%。

圖10.每個開關節點的每個通道之間的相移示意圖。

結論

為5G電信應用構建電源存在挑戰性。這些應用需要快速、大電流瞬態響應,以實現最小峰峰輸出電壓,或在負載瞬態期間實現最短恢復時間。應對這些挑戰的一種簡單方法是:將多個Silent Switcher 3架構(例如LT8627SP)功率轉換器并聯到單個交錯系統中,以此增大電源的帶寬和負載能力,使其獲得執行快速、大電流瞬態的能力。

關于ADI公司

Analog Devices, Inc. (NASDAQ: ADI)是全球領先的半導體公司,致力于在現實世界與數字世界之間架起橋梁,以實現智能邊緣領域的突破性創新。ADI提供結合模擬、數字和軟件技術的解決方案,推動數字化工廠、汽車和數字醫療等領域的持續發展,應對氣候變化挑戰,并建立人與世界萬物的可靠互聯。ADI公司2022財年收入超過120億美元,全球員工2.4萬余人。攜手全球12.5萬家客戶,ADI助力創新者不斷超越一切可能。更多信息,請訪問www.analog.com/cn。

關于作者

Erik Lamp是ADI公司工業和多市場部門的產品應用工程師,主要負責電源產品。他于2020年獲得圣何塞州立大學電氣工程學士學位,并于同年加入ADI公司開始其職業生涯。

Xinyu Liang是ADI公司工業和多市場部門的應用工程經理,主要負責電源產品。他于2018年獲得美國北卡羅來納州立大學電氣工程博士學位,并在畢業后于2019年開啟在ADI公司的職業生涯。

粵公網安備 44030902003195號

粵公網安備 44030902003195號