1前言

軟件無線電(Software Radio)是隨著計算機技術和高速數字信號處理技術的發展迅速而發展起來的。其基本思想是將寬帶A/D及D/A變換器盡可能地靠近天線,將電臺的各種功能用一個開放性、模塊化平臺上的軟件實現。軟件無線電的出現使得無線電技術由以硬件為主的時代走向了以軟件為主的時代。事實上,它是繼模擬通信技術、數字通信技術之后的第三代無線通信技術。

現代通信無論是有線還是無線,一般都采用集中交換方式在用戶間通過交換和傳輸來實現點對點或點對多點的通信,但在有些特殊環境下,分布式交換系統在安全和可靠性方面獨具魅力。本文論述的通信系統就是基于這種思想設計的。該數字通信系統在蜂窩移動電話通信的基礎上將FDM/FDMA,TDMA、程控交換、信道掃描和分配等技術綜合為一體,因而是一種全新的有線通信產品。它不需要中央控制交換機,即可在同一對饋線上實現多對用戶的自動交換和通話。所有用戶終端都是基于分布智能原理而實現的,即每一用戶都有通信接入/撤除的支配權。因而,該系統具有廣泛的應用前景。圖1為該系統的基本網絡結構圖。

2通信終端的線路接口設計

2.1通信終端的基本功能介紹

通信終端是網絡上的主要設備,每一通信電話都有接入和拆除的主動權。同時不影響其它設備的正常工作。通信終端可實現語音、數據、傳真等多種業務接入。

通信終端的主要技術是軟件技術,即利用DSP和MPU等先進技術,并通過軟件來實現盡可能多的硬件工作,從而使設備的可靠性和靈活性大大提高,其通信終端的基本功能框圖如圖2所示。其中的DSP模塊可實現信道掃描、自適應均衡、調制解調、信道濾波、糾錯和加密、數據適配和功率控制等功能。系統管理和控制 MPU模塊則可用來實現信令管理、數據接口、系統狀態管理等功能。語音處理接口模塊的作用是進行語音壓縮處理。數據接口模塊可實現與RS232接口的電平適配。系統中的供電系統包括DC/DC轉換和電壓監視等。

由于本系統的通信信道是某特殊雙絞線,衰減率約20dB/km,因此,在信號傳輸10km以上時,會產生近100dB的衰減,因此,通信信道將變得非常惡劣。但它的信道幅頻特性衰減比較小,并主要分布在中頻。

上述的信道特點決定了該數字通信系統終端線路特殊的接口電路設計。

2.2數字通信終端的線路接口

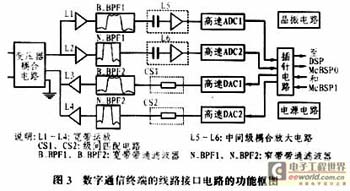

由于該數字通信系統終端采用的是實時全雙工通信,因此其接口電路必須具有收發兩個通道。另外,該通信系統采用的是共路信令,因此其信令信道和話音信道是分開的,它們之間存在一定的保護帶。所以,線路接口電路主要由信令的兩路收發通道和話音的兩路收發通道組成。圖3所示是該數字通信終端接口電路的功能框圖。圖中,從變壓器耦合電路進來的信號經L1→B_BPF1→L5→ADC1和從插針電路進來的信號經DAC1→CS1→B_BPF2→L3分別組成話音信道的收發通道;而從變壓器耦合電路進來的信號經L2→N_BPF1→L6→ADC2和從插針電路進來的信號經 DAC2→CS2→N_BPF2→L4則分別組成了信令信道的收發通道。

3通信終端線路接口的實現

3.1寬帶帶通濾波電路

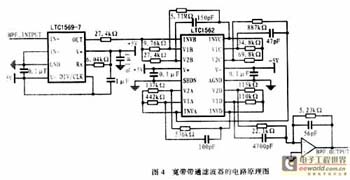

由于信道的衰減很大(20dB/km),因此在傳輸距離較長(如達到 4km)時,信號在到達接收機輸入端時將有很大(80dB)的衰減,這樣,信號將被淹沒在噪聲中,故須用一個阻帶衰減至少為60dB的帶通濾波器來濾除帶外噪聲,以提高輸入信噪比(SNR),從而減小后面軟件處理(信道均衡、上下統采用的是共路分開的,因此,信鄰信道干擾),同擾,因此,必須分別用兩個不同帶寬的帶通濾波器將它們分別從信道中取出,這兩個濾波器的作用除了濾除帶外噪聲外,也可同時抑制相鄰信道信號的干擾,以提高各自的輸入信噪比(SINR)。此外,ADC對模擬信號的采樣將使信號的頻譜產生周期拓延,故須用帶通濾波器對話音和信令信號的頻譜加以限制以使拓延后的信號頻譜不會發生混疊,同時,濾波器也可起到防混疊的作用。

本系統所選用的通用濾波芯片LTC1562在一片芯片內部集成了4個兩階濾波器,每個濾波器的中心頻率可調范圍為10kHz~150kHz。 LTC1562無需外部輸入時鐘,通過外接電阻和電容便可構成低通(LOWPASS)、帶通(BANDPASS)和高通(HIGHPASS)濾波器,其中心頻率(f0)、品質因素(Q)和增益(GAIN)可用電阻編程設置,該芯片既可采用單電源(+5V)供電,也可用雙電源(±5V)供電。LTC1562以其上述特性完全可以在本系統中用來構成窄帶帶通濾波器(帶寬為幾kHz)和寬帶帶通濾波器的高通濾波部分,圖4為寬帶帶通濾波器的實際電路。

低通濾波芯片LTC1569-7可工作在+5V單電源條件下,其截止頻率可達300kHz,并可通過一個外接電阻改變濾波器的截止頻率。該芯片內部集成了一個10階的線性相位濾波器。由于截止頻率在200kHz以上時,利用LTC1569-7構成低通濾波器具有比通用濾波器LTC1562 更好的特性,因此,本設計選用它作為低通濾波器。

3.2 ADC的電路

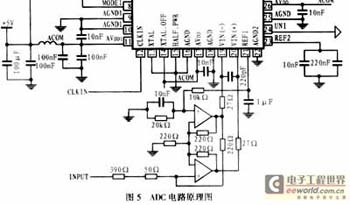

雖然話音信號的帶寬是位于中頻部分(20kHz~200kHz),相對較寬(200kHz),但其中夾雜著大量的帶內噪聲,因此必須使用一個高速ADC(根據那奎斯特第一采樣定理,該 ADC的采樣速率必須達到500ksps,同時為了提供一定的冗余量,本系統選取的ADC芯片的最高輸出采樣速率也應達到1.2Msps)來將模擬信號轉換為數字信號。另外,片內采用Σ-Δ調制的ADC也能對帶內噪聲起到良好的抑制作用,這種擬制主要通過對帶內噪聲整形及片內濾波器來實現,所以,高速采樣 Σ-Δ調制ADC是本系統的首選。

系統中的高速ADC可選擇分辨率為16位的Σ-ΔADC芯片AD7723。該器件的過采樣率有 32/16×Fs可供選擇(本系統采用32×Fs的過采樣率)。它采用單+5V電源,片內參考為2.5V;并具有并行輸出和串行輸出兩種方式,在輸出字速率達1.2MHz的情況下,其輸入信號的帶寬可達 460kHz,同時能向DSP(TMS320VC5410)的McBSP提供時鐘信號、幀同步信號和數據流信號,因此,該高速ADC能夠和DSP組成高速數據采集系統。圖5是其電路連接圖。

3.3 DAC電路

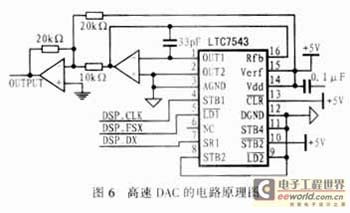

高速DAC可選用分辨率為12位的LTC7543,該芯片的信號轉換穩定時間(settling time)典型值為0.25μs,最大值為1μs。LTC7543采用+5V單電源供電并具有和DSP(TMS320VC5410)的McBSP相兼容的時鐘信號、幀同步信號和數據流信號輸入引腳,輸出信號可采用雙極性輸出,也可以采用單極性輸出(本系統采用前者)。LTC7543的外圍電路比較簡單,圖 6是其電路連接圖,它由兩個寬帶運放,一個外部參考電壓,一個電源濾波電容,一個輸出濾波電容和若干電阻組成。

3.4晶振電路

晶振電路選用的主要器件如圖7 所示,該電路包括32MHz的有源晶體振蕩器、74HC393二進制分頻器和74HC08邏輯與門。其中 74HC393用來產生高速ADC的時鐘輸入信號和幀同步信號;74HC08用來調整幀同步信號的脈寬,以使其與時鐘信號的脈寬大小一致。

4結束語

以上所選的主要器件組成的電路均已做成PCB(印刷電路板),并通過信號測試。測試結果表明:窄帶帶通濾波器(N_BPF1、N_BPF2)的阻帶衰減為 40dB;寬帶帶通濾波器(B_BPF1、B_BPF2)的阻帶衰減為60dB;同時通過高速ADC完全可以實現對500kHz模擬信號的采樣、量化和編碼。

粵公網安備 44030902003195號

粵公網安備 44030902003195號