1 引言

軟件無線電主要由天線、射頻前端、寬帶A/D和D/A轉換器、數(shù)字信號處理器(DSP)及各種軟件組成。軟件無線電體系結構的一個重要特點是將A/D和D/A盡量靠近射頻前端。為減少模擬環(huán)節(jié),在較高的中頻、甚至直接對射頻信號進行數(shù)字化,后面所有功能都由軟件或數(shù)字硬件實現(xiàn)。軟件無線電通信系統(tǒng)要求ADC具有高速度、高精度和寬帶輸入信號范圍。

主要依靠一攬子電阻網(wǎng)絡來保證量化精度的傳統(tǒng)ADC,其精度不可能做得很高,其高端的非線性難以避免。那么,能不能減輕對電阻網(wǎng)絡的依賴轉而依靠數(shù)字信號處理技術來提高精度呢?答案是肯定的,但必須減少量化的帶內噪聲。于是,Σ-Δ ADC和Σ-Δ DAC便應運而生了。

Σ-Δ A/D轉換技術的實質是盡量降低模擬電路的復雜程度,減少帶內的量化噪聲,然后采用數(shù)字信號處理和VLSI技術相結合的方法來提高信號處理精度,增加動態(tài)范圍。下面詳細討論Σ-Δ A/D轉換技術。

2 Σ-Δ A/D轉換技術

2.1 Σ-Δ A/D轉換器的基本原理

2.2.1 A/D轉換中的混疊噪聲和量化噪聲

一般認為,傳統(tǒng)ADC的量化噪聲可作如下近似:

![]()

其中,q為量化臺階,b為量化位數(shù)。相應的噪聲譜密度為:

![]()

可見,量化位數(shù)b越多,量化噪聲功率越小,采樣頻率fs越高,分布在基帶內的噪聲越少。

2.2.2 低通Σ-Δ A/D轉換器的基本原理

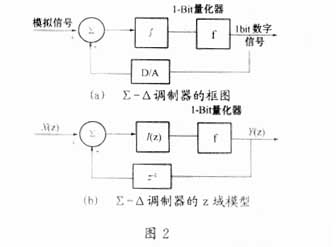

低通Σ-Δ A/D量化是在量化的基礎上發(fā)展而來的,Σ-Δ ADC組成框圖如圖1所示。

它與傳統(tǒng)A/D轉換器的最大不同在于量化過程。后者取樣與量化值是一一對應的,而前者幾乎完全拋開了這一點。

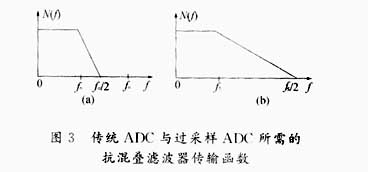

圖2 (a)是一個典型的Σ-Δ低通調制器的原理框圖,圖2(b)是Σ-Δ低通調制器的Z域模型。

待量化的模擬信號與Σ-Δ調制后的1bit輸出信號相差后,送到積分器中,進行1bit量化,從而得到采樣率為fs的1bit流,該1bit流包含了原始模擬信號的大部分特性。隨后,系統(tǒng)把該1bit流送給后面的數(shù)字抽取器,由數(shù)字抽取器從這些粗糙的量化數(shù)據(jù)中重構出低采樣率的高分辨率數(shù)字信號。由于該方法采用1bit量化,因而硬件結構簡單。由于采樣頻率很高,因而對前端模擬抗混疊濾波器的要求大大降低。而這兩方面的因素正是解決傳統(tǒng)A/D轉換器分辨率難以提高的關鍵。對傳統(tǒng)的并行A/D轉換器而言,采樣頻率每增加一倍,信噪比改善約為3dB,相當于0.5位的量化位數(shù)。而Σ-Δ轉換器則為:采樣頻率每增加一倍,信噪比改善約為9dB,相當于1.5位的量化位數(shù)。這就是說,要達到相的量化信噪比,Σ-Δ轉換器與普通A/D轉換器相比,所需的采樣率要低得多。

歸納起來,Σ-Δ調制器性能主要得益于過采樣(Oversampling)、噪聲整形(Noise Shaping)及抽取(Decimation)。

(1)過采樣

過采樣是Σ-Δ調制器以速度換精度的前提。過采樣帶來的好處是:減少了基帶內的量化噪聲。由式(1),分布在基帶內的噪聲功率為:

![]()

一般地,fb≤fs,因此,基帶內的噪聲能量被大大降低。應該指出,這只是在不計Σ-Δ調制的情況下,僅由采樣率fs提高帶來的量化噪聲減小。如果計及由Σ-Δ調制帶來的量化噪聲向高頻端的推移,則基帶噪聲功率會進一步減小。

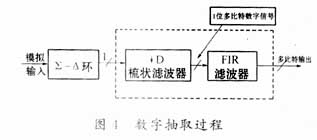

過采樣帶來的另一個好處是:降低了對前端抗混疊模擬濾波器的要求。傳統(tǒng)ADC與過采樣ADC所需的抗混疊濾波器傳輸函數(shù)分別如圖3(a)和圖3(b)所示。

傳統(tǒng)ADC的防混濾波器過渡帶為fn/2-fb,而過采樣ADC的防混濾波器過渡帶為fs/2-fb, 但fsfb,故,過采樣ADC的防混濾波器過渡帶比傳統(tǒng)ADC的寬很多。既然過渡帶與通帶之比決定了濾波器的復雜性,因此,過采樣ADC對防混濾波器的要求非常簡單。例如,對fs/fn=64,一個簡單的RC低通濾波器就足夠了。

(2)噪聲整形

噪聲整形是Σ-Δ調制器提高輸出SNR(信噪比)的關鍵。Σ-Δ調制器能將低頻量化噪聲調制到高頻段,改變噪聲分布,這就是噪聲整形的由來。

噪聲整形大大增加了過采樣效果,即用提高工作采樣頻率換取量化精度的效果。因此,只要濾除了帶外的量化噪聲,就能夠從1bit流中有效地用速度換取精度。這正是Σ-Δ轉換器獲取高分辨率的原理所在。

(3) 數(shù)字抽取

濾除將要折疊到基帶中的噪聲是數(shù)字濾波級的主要任務,去除量化噪聲也就相當于提高了數(shù)字輸出的有效精度,即把1bit數(shù)據(jù)重構成多bit數(shù)據(jù)。同時,它還要把過高的采樣率降下來。

調制器的輸出是模擬輸入的粗糙量化。然而,調制器是在奈奎斯特頻率的N倍上進行采樣的。故,高精度可以通過平均這N個點而獲得。平均過程相當于頻域的低通濾波。其抽取過程可按圖4進行。

用單一系數(shù)的梳狀濾波器作抽取器的第一級可以極大地節(jié)約時間,但是,它并不能有效去除大部分帶外量化噪聲,因此,實用中都需再加一個FIR數(shù)字濾波器。

這樣,過采樣、噪聲整形和數(shù)字濾波方法的有機結合就可以克服現(xiàn)有VLSI技術難以制作噪聲容限小的模擬電路之不足,在無需附加工藝的情況下,利用元件精度和匹配要求低的“Σ-Δ量化器”來實現(xiàn)高分辨率的A/D轉換。

3 高階Σ-Δ A/D轉換技術

Σ-Δ A/D轉換器的基帶噪聲比奈奎斯特采樣器或Δ調制器的要小得多。但是,對前述的一階Σ-Δ調制器,其基帶噪聲并不能降到低于10比特A/D轉換器所要求的60dB的SNR要求。因此,要想盡量減少基帶內的量化噪聲,只有增加采樣頻率。但是,采樣頻率的增加受到電路工作頻率和數(shù)字濾波器性能的制約。據(jù)此,為了增加噪聲整形效果以便降低所需的采樣頻率,在一階Σ-Δ調制器的基礎上發(fā)展了各種各樣的高階Σ-Δ調制器。

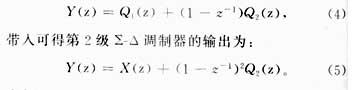

下面,我們先討論二階Σ-Δ調制器。既然這些層疊結構使用噪聲前饋的方案,因此,系統(tǒng)總是穩(wěn)定的。當多級一階Σ-Δ回路疊用以獲得高階調制器時,傳向后續(xù)回路的信號是當前回路的噪聲。這個噪聲是積分器輸出與量化器輸出的差值。

如果輸入到第2和第3級Σ-Δ回路的信號分別是Q1,Q2,則第2級Σ-Δ調制器的量化輸出為:

類似地,對于3階ΣΔ調制器,

這里,Q3是第3級Σ-Δ調制器的量化噪聲。

分析表明,3階Σ-Δ調制器的帶內量化噪聲明顯比1階的小。

我們用Matlab語言對低通Σ-Δ A/D轉換過程進行了仿真,得到的結果與理論分析十分相符(3階環(huán),輸出SINAD約為108dB)。其主要程序略。

4 結束語

上面, 我們對低通Σ-Δ A/D轉換技術作了較為詳細的分析。國外從八十年代后期開始大規(guī)模地對Σ-Δ A/D和Σ-Δ D/A轉換技術展開研究,目前,已有成熟的Σ-Δ ADC和Σ-ΔDAC產品。

參考文獻

1 楊小牛等編著.軟件無線電原理與應用.北京:電子工業(yè)出版社,2001

2 鈕心忻等編著.軟件無線電技術與應用.北京:北京郵電大學出版社,2001

粵公網(wǎng)安備 44030902003195號

粵公網(wǎng)安備 44030902003195號