射頻識(shí)別技術(shù)已被應(yīng)用到許多領(lǐng)域,如護(hù)照、交通運(yùn)輸、產(chǎn)品追蹤、汽車(chē)以及動(dòng)物識(shí)別等。射頻識(shí)別即RFID(Radio Frequency IDentification)技術(shù),又稱(chēng)電子標(biāo)簽、無(wú)線射頻識(shí)別,是一種通信技術(shù),可通過(guò)無(wú)線電訊號(hào)識(shí)別特定目標(biāo)并讀寫(xiě)相關(guān)數(shù)據(jù),而無(wú)需識(shí)別系統(tǒng)與特定目標(biāo)之間建立機(jī)械或光學(xué)接觸。射頻識(shí)別技術(shù)(Radio Frequency Identification,縮寫(xiě)RFID),射頻識(shí)別技術(shù)是20世紀(jì)90年代開(kāi)始興起的一種自動(dòng)識(shí)別技術(shù),射頻識(shí)別技術(shù)是一項(xiàng)利用射頻信號(hào)通過(guò)空間耦合(交變磁場(chǎng)或電磁場(chǎng))實(shí)現(xiàn)無(wú)接觸信息傳遞并通過(guò)所傳遞的信息達(dá)到識(shí)別目的的技術(shù)。從信息傳遞的基本原理來(lái)說(shuō),射頻識(shí)別技術(shù)在低頻段基于變壓器耦合模型(初級(jí)與次級(jí)之間的能量傳遞及信號(hào)傳遞),在高頻段基于雷達(dá)探測(cè)目標(biāo)的空間耦合模型(雷達(dá)發(fā)射電磁波信號(hào)碰到目標(biāo)后攜帶目標(biāo)信息返回雷達(dá)接收機(jī))。1948年哈里斯托克曼發(fā)表的"利用反射功率的通信"奠定了射頻識(shí)別技術(shù)的理論基礎(chǔ)。

由于RFID標(biāo)簽芯片及其控制器要求具有低成本、低功耗的特性,目前定義RFID產(chǎn)品的工作頻率有低頻、高頻和超高頻的頻率范圍內(nèi)的符合不同標(biāo)準(zhǔn)的不同的產(chǎn)品,而且不同頻段的RFID產(chǎn)品會(huì)有不同的特性。其中感應(yīng)器有無(wú)源和有源兩種方式,因此本文提出一種符合ISO18000-6B協(xié)議,并滿(mǎn)足低成本、低功耗要求的高頻RFID標(biāo)簽芯片數(shù)字基帶處理器的設(shè)計(jì)。

1、數(shù)字系統(tǒng)結(jié)構(gòu)圖

根據(jù)ISO18000-6B協(xié)議,從閱讀器到應(yīng)答器的數(shù)據(jù)傳送通過(guò)對(duì)載波的幅度調(diào)制(ASK)完成,數(shù)據(jù)編碼為通過(guò)生成脈沖創(chuàng)建的曼徹斯特碼編碼,速率為40 kb/s;標(biāo)簽返回給閱讀器的數(shù)據(jù)通過(guò)FM0編碼調(diào)制后發(fā)送至模擬前端,經(jīng)由天線發(fā)送至閱讀器。

所設(shè)計(jì)的數(shù)字系統(tǒng)結(jié)構(gòu)圖如圖1所示,主要完成以下功能:(1)對(duì)前向鏈路解調(diào)輸出信號(hào)進(jìn)行曼徹斯特碼解碼,給出解碼輸出時(shí)鐘,解析出再同步信號(hào);(2)對(duì)解碼出的數(shù)據(jù)進(jìn)行CRC校驗(yàn),確認(rèn)數(shù)據(jù)傳輸和標(biāo)簽解調(diào)的正確性,并且同時(shí)對(duì)解碼輸出數(shù)據(jù)進(jìn)行串并轉(zhuǎn)換,以及解析出正確的命令;(3)根據(jù)ISO18000-6B協(xié)議的全部功能要求對(duì)接收的指令進(jìn)行正確處理;(4)根據(jù)協(xié)議的要求對(duì)存儲(chǔ)器進(jìn)行正確讀寫(xiě)操作;(5)對(duì)處理完畢的數(shù)據(jù)進(jìn)行組織,生成CRC校驗(yàn)碼;(6)對(duì)回送數(shù)據(jù)進(jìn)行FMO編碼,回送給射頻模擬前端進(jìn)行調(diào)制。

在設(shè)計(jì)中,有限狀態(tài)機(jī)的設(shè)計(jì)是數(shù)字部分設(shè)計(jì)的核心,其功能是協(xié)調(diào)模塊之間數(shù)據(jù)與信號(hào)交互、處理接收到的指令及其相應(yīng)的數(shù)據(jù)、轉(zhuǎn)換自身狀態(tài)、執(zhí)行對(duì)碰撞計(jì)數(shù)器和靜默計(jì)數(shù)器的操作、執(zhí)行對(duì)存儲(chǔ)器的讀寫(xiě)存儲(chǔ)操作、規(guī)定反向散射標(biāo)簽的64位UID以及MTP存儲(chǔ)器內(nèi)容,并和外圍模塊電路一起構(gòu)成防碰撞電路,實(shí)現(xiàn)防碰撞算法。

2、低功耗設(shè)計(jì)

電路中耗散的能量可以分為靜態(tài)功耗和動(dòng)態(tài)功耗。形成靜態(tài)功耗的主要原因是晶體管中從源極到漏極的亞閾值泄漏,就是指閾值電壓的降低阻止了柵的關(guān)閉。動(dòng)態(tài)功耗分為開(kāi)關(guān)功耗和內(nèi)部功耗。開(kāi)關(guān)功耗是由于器件輸出端的負(fù)載電容的充放電引起的。

數(shù)字部分實(shí)現(xiàn)低功耗,可以從系統(tǒng)級(jí)和RTL代碼級(jí)兩方面考慮。本設(shè)計(jì)中采取降低功耗的有效措施包括:降低電源電壓,降低時(shí)鐘頻率,門(mén)控時(shí)鐘技術(shù),組織模塊的設(shè)計(jì)方法。

2.1同步化不同時(shí)鐘的設(shè)計(jì)方案

當(dāng)系統(tǒng)中有兩個(gè)或兩個(gè)以上不同時(shí)鐘時(shí),數(shù)據(jù)的建立和保持時(shí)間很難得到保證,會(huì)面臨復(fù)雜的時(shí)間問(wèn)題。最好的方法是將不同的時(shí)鐘同步化,由于標(biāo)簽數(shù)字基帶電路中的編碼器設(shè)計(jì)中需要編碼輸入時(shí)鐘160 kHz和編碼輸出時(shí)鐘320 kHz,所以不同的觸發(fā)器使用不同的時(shí)鐘。為了系統(tǒng)穩(wěn)定,用系統(tǒng)時(shí)鐘1.28 MHz將160 kHz和320 kHz時(shí)鐘同步化,如圖2所示。1.28 MHz的高頻時(shí)鐘將作為系統(tǒng)時(shí)鐘,輸入到所有觸發(fā)器的時(shí)鐘端。160 MHz _EN和320 MHz_EN將控制所有觸發(fā)器的使能端。即原來(lái)接160 MHz時(shí)鐘的觸發(fā)器,接1.28 MHz時(shí)鐘,同時(shí)160 MHz_EN將控制該觸發(fā)器使能,原接320 MHz時(shí)鐘的觸發(fā)器,也接1.28 MHz時(shí)鐘,同時(shí)320 MHz_EN將控制該觸發(fā)器使能。

2.2降低電源電壓

動(dòng)態(tài)功耗和電源電壓的平方成正比,故降低電源電壓是減少功耗的有效辦法,但是降低供電電壓,會(huì)帶來(lái)很多副作用:首先,降低供電電壓,會(huì)導(dǎo)致速度下降,減小電容充放電的電流或負(fù)載驅(qū)動(dòng)電流;其次,會(huì)導(dǎo)致較低的輸出功率或較低的信號(hào)幅度,從而產(chǎn)生噪聲和信號(hào)衰減的問(wèn)題。研究表明:降低閥值電壓,可以使得動(dòng)態(tài)功耗減少,但會(huì)增大靜態(tài)功耗。

設(shè)計(jì)中采用的是臺(tái)積電提供的0.18μm數(shù)字標(biāo)準(zhǔn)單元,標(biāo)準(zhǔn)工作電壓為0.9 V~1.1 V.而EEPROM工作電壓為0.9 V~1.2 V@讀數(shù)據(jù)/1.8 V@寫(xiě)數(shù)據(jù),所以進(jìn)行寫(xiě)操作時(shí)需要用到電平轉(zhuǎn)換將1.0 V轉(zhuǎn)換到1.8 V的電壓,以便進(jìn)行數(shù)據(jù)的交互。

2.3門(mén)控時(shí)鐘的設(shè)計(jì)

為了降低芯片的功耗,設(shè)計(jì)中使用了門(mén)控時(shí)鐘:用使能信號(hào)控制寄存器的時(shí)鐘端,當(dāng)使能信號(hào)有效時(shí)時(shí)鐘翻轉(zhuǎn),否則時(shí)鐘保持在固定電平。因此時(shí)鐘使能可以將電路中的部分電路處于空閑狀態(tài),阻止寄存器內(nèi)部翻轉(zhuǎn)和寄存器之間組合邏輯開(kāi)關(guān)動(dòng)作,以達(dá)到節(jié)省功耗的目的。圖3所示為門(mén)控時(shí)鐘的設(shè)計(jì)方案。

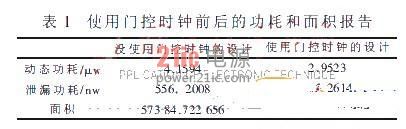

表1給出利用綜合工具Design Compiler對(duì)當(dāng)前設(shè)計(jì)進(jìn)行綜合后的功耗和面積報(bào)告。可以看出,本設(shè)計(jì)使用門(mén)控時(shí)鐘后,總的動(dòng)態(tài)功耗降低了很多,并且在降低功耗的同時(shí),面積也有了一定的減小。

2.4組織模塊設(shè)計(jì)方法

由于在設(shè)計(jì)中并不是所有的模塊都同時(shí)工作,而是在某一個(gè)狀態(tài)下,只開(kāi)啟一個(gè)或幾個(gè)模塊,其他模塊處于關(guān)閉狀態(tài),所以如果有效組織模塊的開(kāi)關(guān),將會(huì)減少寄存器的開(kāi)關(guān)翻轉(zhuǎn)動(dòng)作。設(shè)計(jì)中利用有限狀態(tài)機(jī)根據(jù)不同的指令和狀態(tài)轉(zhuǎn)換開(kāi)啟不同的模塊來(lái)完成數(shù)據(jù)的處理要求和存儲(chǔ)操作:當(dāng)接收前向數(shù)據(jù)時(shí),開(kāi)啟編碼器、CRC計(jì)算/校驗(yàn)、和串并轉(zhuǎn)換;當(dāng)處理數(shù)據(jù)時(shí),開(kāi)啟模塊有限狀態(tài)控制機(jī)、EEPROM控制模塊、靜默計(jì)數(shù)器、隨機(jī)數(shù)產(chǎn)生器;當(dāng)返回?cái)?shù)據(jù)時(shí),開(kāi)啟模塊有限狀態(tài)控制機(jī)、EEPROM控制模塊、數(shù)據(jù)輸出控制端、編碼器其他模塊關(guān)閉。

3、芯片測(cè)試

首先采用FPGA完成芯片的功能驗(yàn)證,以FPGA的可編程邏輯陣列為基本單元,實(shí)現(xiàn)ISO18000-6B的數(shù)字基帶功能的硬件仿真驗(yàn)證。然后使用ASIC芯片設(shè)計(jì)EDA工具將RTL頂層描述映射為基于TSMC提供的目標(biāo)工藝庫(kù)的基本數(shù)字單元的物理電路,并生成CAD版圖且提交給TSMC半導(dǎo)體工廠制作出來(lái)。

進(jìn)行芯片測(cè)試時(shí),利用先施閱讀器產(chǎn)生RFID各種命令信號(hào),經(jīng)解調(diào)后輸入到待測(cè)試芯片的數(shù)據(jù)輸入端。芯片在電源、時(shí)鐘源信號(hào)、復(fù)位信號(hào)的共同激勵(lì)下進(jìn)入正常工作狀態(tài)并對(duì)輸入命令數(shù)據(jù)進(jìn)行響應(yīng),將數(shù)據(jù)輸出到調(diào)制電路,然后反射回閱讀器。閱讀器根據(jù)接收到的信號(hào)決定下一步操作。在閱讀器和待測(cè)芯片的交互過(guò)程中,可用邏輯分析儀觀察中間過(guò)程。圖4為先施閱讀器對(duì)測(cè)試芯片發(fā)送read命令時(shí),用邏輯分析儀捕捉的內(nèi)部信號(hào),其中信號(hào)data_in為解調(diào)器解調(diào)出的前向鏈路數(shù)據(jù),信號(hào)data_out為芯片的返回?cái)?shù)據(jù)。

從已流片芯片的測(cè)試結(jié)果看,標(biāo)簽芯片數(shù)字系統(tǒng)的設(shè)計(jì)很好地完成了符合ISO18000-6B協(xié)議的所有強(qiáng)制命令以及讀寫(xiě)操作和鎖存、查詢(xún)鎖存等基本功能,且在閱讀器存盤(pán)操作下的平均速率為45~60張/s,功耗為3.10μW,很好地完成了低功耗無(wú)源電子標(biāo)簽的設(shè)計(jì)。

粵公網(wǎng)安備 44030902003195號(hào)

粵公網(wǎng)安備 44030902003195號(hào)