引言

UHF RFID讀寫(xiě)器具有讀寫(xiě)距離遠(yuǎn)、讀寫(xiě)速度快等優(yōu)點(diǎn),已成功運(yùn)用于供應(yīng)鏈管理、航空管理和后勤管理等諸多領(lǐng)域。本設(shè)計(jì)依據(jù)的協(xié)議是EPC C1G2(EPCClassl Generation2)。

本文介紹了一種讀寫(xiě)器的編解碼部分由FPGA來(lái)完成的設(shè)計(jì)方案,由FPGA負(fù)責(zé)前向鏈路的PIE編碼和后向鏈路的FM0/miller解碼,且解碼模塊可對(duì)標(biāo)簽突發(fā)傳來(lái)的數(shù)據(jù)立即檢測(cè)并實(shí)施解碼,實(shí)現(xiàn)了較快的解碼速率。FPGA選用的是Altera公司的EP1C3T100C6芯片。

1、RFID系統(tǒng)介紹

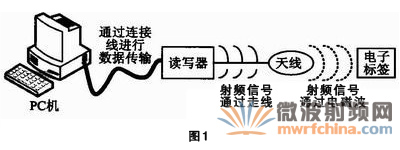

圖1所示為RFID系統(tǒng),主要由PC機(jī)、讀寫(xiě)器、天線和電子標(biāo)簽組成。讀寫(xiě)器與電子標(biāo)簽之間的數(shù)據(jù)通過(guò)天線進(jìn)行傳遞。讀寫(xiě)器作為RFID系統(tǒng)的一部分,既能與標(biāo)簽通信,又能向PC機(jī)傳輸數(shù)據(jù)并執(zhí)行上位機(jī)所要求的操作,具有發(fā)送、接收和處理數(shù)據(jù)的能力。讀寫(xiě)器系統(tǒng)按其所處理信號(hào)的不同,主要由2個(gè)部分組成,即處理數(shù)字信號(hào)的基帶部分和處理模擬信號(hào)的射頻部分。

圖1 RFID系統(tǒng)

2、EPC C1G2協(xié)議的相關(guān)介紹

EPC C1G2標(biāo)準(zhǔn)具有如下特點(diǎn):速度快,速率可達(dá)40~640 kbps;可以同時(shí)讀取標(biāo)簽的數(shù)量多,理論上能讀到1000多個(gè)標(biāo)簽;可在密集的讀寫(xiě)器環(huán)境下工作,能迅速使用變化無(wú)常的標(biāo)簽群;存儲(chǔ)區(qū)域多,可延伸使用用戶的內(nèi)存需求;功能強(qiáng),具有多種寫(xiě)保護(hù)方式,安全性強(qiáng);通用性強(qiáng),符合EPC規(guī)則;產(chǎn)品價(jià)格低,兼容性好。

2.1 PIE編碼介紹

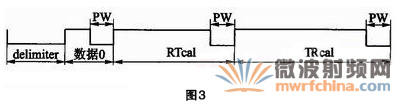

EPC C1G2協(xié)議規(guī)定發(fā)送鏈路(即讀寫(xiě)器向標(biāo)簽發(fā)送數(shù)據(jù))采用的編碼方式是脈沖間隔編碼(即PIE編碼)。讀寫(xiě)器每次給標(biāo)簽發(fā)送命令,都以幀同步碼或前同步碼開(kāi)始所有的通信。幀同步碼格式如圖2所示,幀同步碼由delimiter、數(shù)據(jù)0和RTcal三部分組成。前同步碼格式如圖3所示,前同步碼由delimiter、數(shù)據(jù)0、RTcal和TRcal四部分組成,除delimiter外,各部分均以低脈沖PW結(jié)尾,且各部分PW的長(zhǎng)度必須相同。de limiter的長(zhǎng)度固定為12.5μs,協(xié)議規(guī)定允許有±5%的誤差。delimiter用于給電子標(biāo)簽校準(zhǔn)時(shí)鐘。

圖2 PIE編碼的0和1

圖3 PIE前同步碼

前同步碼只用于表明盤(pán)存周期開(kāi)始的Query命令中,其他命令則以幀同步碼開(kāi)始。當(dāng)Query命令數(shù)據(jù)中的DR=1、前同步碼中的TRcal長(zhǎng)度為33.3μs時(shí),可設(shè)定反向鏈路(即標(biāo)簽向讀寫(xiě)器發(fā)送數(shù)據(jù))頻率最高為640kHz。

2.2 FM0和miller碼介紹

Query命令中M參數(shù)值決定了標(biāo)簽返回?cái)?shù)據(jù)的編碼方式,即FM0、miller2、miller4、miller8四種。FM0碼在每個(gè)數(shù)據(jù)邊界處和數(shù)據(jù)0中間反相。miller碼則是在兩個(gè)連續(xù)的數(shù)據(jù)0的邊界處和數(shù)據(jù)1的中間反相。miller編碼序列每位可包含2、4、8個(gè)副載波周期,即miller2、mille r4、miller8三種編碼形式。這四種編碼方式都以各自特定的幀頭開(kāi)始,而具體選擇哪種幀頭,則由Query命令中Trext參數(shù)值決定,并且在結(jié)尾處都有一位“dummyl”作為數(shù)據(jù)傳送的結(jié)束標(biāo)志。

2.3 讀寫(xiě)器與標(biāo)簽通信流程

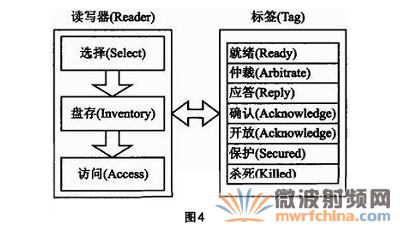

EPC C1G2協(xié)議規(guī)定讀寫(xiě)器的命令分為選擇、盤(pán)存、訪問(wèn)3類,而標(biāo)簽的工作狀態(tài)分為就緒、仲裁、應(yīng)答、確認(rèn)、開(kāi)放、保護(hù)、殺死7個(gè)狀態(tài),讀寫(xiě)器命令類型和標(biāo)簽狀態(tài)如圖4所示。讀寫(xiě)器依賴3類命令通過(guò)改變標(biāo)簽所處的狀態(tài),實(shí)現(xiàn)對(duì)標(biāo)簽群的篩選,以及對(duì)單個(gè)標(biāo)簽的識(shí)別和訪問(wèn)過(guò)程。讀寫(xiě)器與標(biāo)簽的通信過(guò)程略一編者注。

圖4 讀寫(xiě)器命令類型和標(biāo)簽狀態(tài)

3、總體設(shè)計(jì)

在本讀寫(xiě)器設(shè)計(jì)中,ARM與FPGA協(xié)同工作。ARM芯片是LPC2148,工作時(shí)鐘是20 MHz,主要完成對(duì)讀寫(xiě)器系統(tǒng)的控制。而FPGA則負(fù)責(zé)編解碼部分的數(shù)據(jù)流處理,工作時(shí)鐘頻率是25 MHz。圖5是FPGA部分的整體設(shè)計(jì)框圖。

圖5 整體設(shè)計(jì)框圖

FPGA中的模塊主要包括協(xié)議控制及命令產(chǎn)生模塊、PIE編碼模塊、FM0/miller解碼模塊,以及用于與PC機(jī)交互的串口控制模塊。

工作過(guò)程如下:對(duì)讀寫(xiě)器命令數(shù)據(jù)及其相應(yīng)的CRC5/16校驗(yàn)位進(jìn)行PIE編碼,編碼完成送到射頻發(fā)射端,數(shù)字信號(hào)通過(guò)控制射頻芯片RF2 173的開(kāi)關(guān)引腳實(shí)現(xiàn)調(diào)制深度為100%的OOK(On-Off Keying)調(diào)制,并經(jīng)由收發(fā)分離的定向耦合器,通過(guò)天線發(fā)射出去。

場(chǎng)內(nèi)標(biāo)簽接收到讀寫(xiě)器發(fā)送的信息后,在允許其通信的情況下,會(huì)根據(jù)讀寫(xiě)器發(fā)送來(lái)的命令參數(shù),選擇4種編碼方式中的一種,將要回復(fù)讀寫(xiě)器的數(shù)據(jù)進(jìn)行編碼,經(jīng)調(diào)制之后在空間傳輸。

讀寫(xiě)器天線接收到標(biāo)簽信息后,經(jīng)由定向耦合器將標(biāo)簽信息送到讀寫(xiě)器的射頻接收模塊,該模塊對(duì)標(biāo)簽信息進(jìn)行解調(diào),并將解調(diào)后得到的數(shù)字信號(hào)送給FPGA的FM0/miller解碼模塊。解碼模塊根據(jù)數(shù)據(jù)的編碼方式選擇相應(yīng)的電路解碼,解碼后的數(shù)據(jù)返回給協(xié)議控制及命令產(chǎn)生模塊。該模塊根據(jù)上次發(fā)送的命令以及接收到的標(biāo)簽信息作出判斷,產(chǎn)生下一次的操作命令數(shù)據(jù),發(fā)給PIE編碼模塊,與該標(biāo)簽進(jìn)行進(jìn)一步的信息交互或選擇重新讀取另外的標(biāo)簽。

同時(shí),為了準(zhǔn)確獲取標(biāo)簽信息,必須將讀寫(xiě)器與PC機(jī)相連。讀寫(xiě)器通過(guò)由FPGA實(shí)現(xiàn)的串口模塊與PC機(jī)相連,對(duì)讀取到的標(biāo)簽信息做必要的顯示,如標(biāo)簽返回的RN16、EPC、UII等。

4、FPGA實(shí)現(xiàn)電路

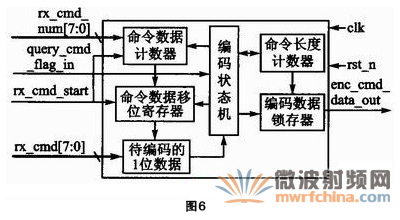

為了實(shí)現(xiàn)FPGA部分的功能,在Altera公司的EP1C3T100C6芯片上,利用Quartus II軟件進(jìn)行設(shè)計(jì),PIE編碼模塊設(shè)計(jì)如圖6所示。

圖6 PIE編碼模塊設(shè)計(jì)框圖

4.1 編碼模塊設(shè)計(jì)

PIE編碼由pie_encode模塊實(shí)現(xiàn)。該模塊接收命令產(chǎn)生模塊并行發(fā)來(lái)的8位數(shù)據(jù),按照協(xié)議規(guī)定及設(shè)置,先給命令數(shù)據(jù)添加特定的幀頭,并根據(jù)數(shù)據(jù)傳輸速率,對(duì)命令數(shù)據(jù)及其CRC5/16校驗(yàn)位進(jìn)行PIE編碼,編碼完成后輸出給射頻發(fā)射模塊調(diào)制,然后通過(guò)天線發(fā)送出去。其設(shè)計(jì)框圖如圖6所示。

PIE編碼模塊由編碼狀態(tài)機(jī)作為控制模塊。狀態(tài)機(jī)的狀態(tài)由命令幀頭和數(shù)據(jù)0和1組成,即idle、delimiter、tari、rtcal、trcal、data_ sendl、data_send0 7個(gè)狀態(tài),其中idle是空閑狀態(tài),接收到開(kāi)始信號(hào)后跳轉(zhuǎn)到其他狀態(tài)。狀態(tài)機(jī)的流程按照命令的組成依次進(jìn)行,每個(gè)狀態(tài)按照協(xié)議要求保持特定的時(shí)間,直至命令編碼完成。由于Query命令和其他命令的幀頭不同,query_cmd_flag_in信號(hào)用于指示此次發(fā)送來(lái)的數(shù)據(jù)是否為Query命令數(shù)據(jù),如果是,則在編碼時(shí)加入TRcal命令段;否則,跳過(guò)TRcal狀態(tài)。

在接收部分?jǐn)?shù)據(jù)開(kāi)始發(fā)送指示信號(hào)rx_cmd_start與要發(fā)送的數(shù)據(jù)rx_cmd、rx_cmd_num保持同步,編碼模塊中的命令數(shù)據(jù)計(jì)數(shù)器和命令數(shù)據(jù)移位寄存器根據(jù)rx_cmd_start信號(hào)將8位數(shù)據(jù)并行送入各自的寄存器。

接收完成后,數(shù)據(jù)寄存器會(huì)根據(jù)計(jì)數(shù)器中的值進(jìn)行相應(yīng)的移位,將無(wú)效數(shù)據(jù)移出,保證有效數(shù)據(jù)是從命令寄存器中的最高位開(kāi)始。同時(shí),每完成一位數(shù)據(jù)的編碼,計(jì)數(shù)器自減1,移位寄存器也自動(dòng)左移一位,將下一個(gè)要編碼的數(shù)據(jù)放入待編碼數(shù)據(jù)寄存器中,該寄存器由此去控制狀態(tài)機(jī)的下一個(gè)流程。

發(fā)送部分主要由一個(gè)命令長(zhǎng)度計(jì)數(shù)器組成,該計(jì)數(shù)器根據(jù)命令參數(shù)的設(shè)置以及所處的狀態(tài)進(jìn)行計(jì)數(shù),控制狀態(tài)機(jī)在某個(gè)狀態(tài)保持的時(shí)間當(dāng)一位數(shù)據(jù)編碼完成,計(jì)數(shù)器清0,并開(kāi)始對(duì)下一位數(shù)據(jù)計(jì)數(shù),同時(shí)狀態(tài)機(jī)也跳轉(zhuǎn)到下一個(gè)狀態(tài),而編碼數(shù)據(jù)則根據(jù)狀態(tài)機(jī)的狀態(tài)以及計(jì)數(shù)器的值拉高或拉低,并由鎖存器將編碼后的命令鎖存輸出。這樣就實(shí)現(xiàn)了邊編碼邊調(diào)制的目的,提升了命令發(fā)送的速率,也節(jié)省了硬件資源。

4.2 解碼模塊設(shè)計(jì)

解碼部分由data_pre_process、fm_and_miller_decode、data_post_decode 3個(gè)模塊組成。data_pre_process是解碼數(shù)據(jù)預(yù)處理模塊,接收射頻模塊解調(diào)后的數(shù)據(jù)。因?yàn)樯漕l發(fā)射和接收使用的是同一根天線,發(fā)射的數(shù)據(jù)信息以及其他雜波信號(hào)經(jīng)常會(huì)泄露進(jìn)解碼模塊。該模塊主要是去除信號(hào)中的毛刺,并對(duì)接收數(shù)據(jù)的高低電平長(zhǎng)度進(jìn)行判斷,看是否符合編碼規(guī)則,如果均在合適的范圍內(nèi),則視為成功。同時(shí)產(chǎn)生待解碼數(shù)據(jù)的采樣信號(hào),以及其他指示信號(hào),以便解碼模塊的數(shù)據(jù)處理;若不符合要求則丟棄這部分?jǐn)?shù)據(jù),重新檢查分析新來(lái)的數(shù)據(jù)信息。

data_post_process是解碼數(shù)據(jù)確認(rèn)及串并轉(zhuǎn)換模塊。解調(diào)后的數(shù)據(jù)經(jīng)過(guò)了解碼預(yù)處理模塊的初步判斷,只是符合了一定的編碼規(guī)則,在解碼過(guò)程中還可能會(huì)出現(xiàn)諸如幀頭出錯(cuò)、結(jié)尾數(shù)據(jù)不為1等其他錯(cuò)誤。該模塊通過(guò)判斷解碼模塊的error和data_success信號(hào),確認(rèn)此次解碼是否成功,若成功,將接收解碼數(shù)據(jù),同時(shí)考慮到串行數(shù)據(jù)傳輸速度較慢,本模塊會(huì)對(duì)解碼數(shù)據(jù)進(jìn)行串并轉(zhuǎn)換,然后8位并行地將解碼后的數(shù)據(jù)傳輸給其他模塊。

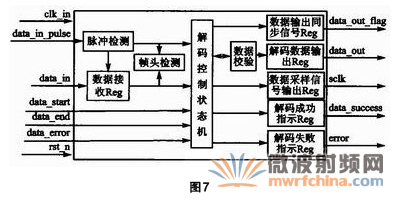

fm_and_miller_decode是解碼模塊。其組成框圖如圖7所示。

圖7 miller2 解碼結(jié)構(gòu)圖

該解碼模塊主要由解碼狀態(tài)機(jī)控制。狀態(tài)機(jī)的狀態(tài)由初始態(tài)、數(shù)據(jù)解碼態(tài),以及最后的解碼成功和解碼失敗狀態(tài)組成。接收到解碼開(kāi)始信號(hào)時(shí),狀態(tài)機(jī)由初始態(tài)跳轉(zhuǎn)到數(shù)據(jù)解碼態(tài)開(kāi)始解碼,在解碼過(guò)程中,如果發(fā)現(xiàn)輸入的數(shù)據(jù)違背了編碼規(guī)則或不符合命令的設(shè)置,則直接跳入失敗狀態(tài)。在該狀態(tài)下,會(huì)有一個(gè)解碼失敗信號(hào)error產(chǎn)生并輸出。如果解碼順利進(jìn)行到結(jié)束,則跳轉(zhuǎn)到解碼成功狀態(tài),會(huì)有一個(gè)解碼成功信號(hào)data_success產(chǎn)生并輸出,控制下一個(gè)模塊的工作。這樣解碼狀態(tài)機(jī)一邊接收待解碼數(shù)據(jù),進(jìn)行解碼處理,一邊將前面處理完的數(shù)據(jù)輸出給CRC5/16校驗(yàn)?zāi)K,實(shí)現(xiàn)了類似于流水線的工作,節(jié)省了解碼時(shí)間。

解碼模塊接收部分通過(guò)采樣信號(hào)接收待解碼數(shù)據(jù),這樣便只需檢測(cè)采樣信號(hào),節(jié)省了計(jì)數(shù)器的消耗。采樣到的數(shù)據(jù)首先進(jìn)行幀頭檢測(cè),判斷使用的幀頭類型及編碼形式,若幀頭檢測(cè)正確,則實(shí)施去幀頭處理,將有效數(shù)據(jù)通過(guò)控制狀態(tài)機(jī)流程來(lái)進(jìn)行解碼。而其他控制信號(hào),即來(lái)自解碼預(yù)處理模塊的數(shù)據(jù)開(kāi)始傳輸指示data_start,數(shù)據(jù)傳輸結(jié)束指示data_end,數(shù)據(jù)傳輸錯(cuò)誤指示data_error則直接控制狀態(tài)機(jī)狀態(tài)的轉(zhuǎn)換。

解碼完成之后,根據(jù)前面發(fā)送命令的類型,對(duì)解碼后的數(shù)據(jù)進(jìn)行CRC5/16校驗(yàn),若校驗(yàn)正確,則去掉校驗(yàn)位,將有效數(shù)據(jù)輸出;若錯(cuò)誤,則返回給狀態(tài)機(jī),發(fā)出解碼錯(cuò)誤指示。同時(shí),根據(jù)狀態(tài)機(jī)所處的特定狀態(tài),在每一個(gè)解碼數(shù)據(jù)期間會(huì)輸出持續(xù)一個(gè)周期的數(shù)據(jù)采樣信號(hào)sclk,以及在數(shù)據(jù)開(kāi)始解碼時(shí)便與解碼數(shù)據(jù)同步輸出的信號(hào)data_out_flag,以便后續(xù)模塊進(jìn)行數(shù)據(jù)的采樣與控制。

5、軟件仿真與硬件測(cè)試

以上各模塊均使用硬件描述語(yǔ)言實(shí)現(xiàn)。在Quartus II9.0中全部編譯通過(guò),滿足時(shí)序要求,編譯報(bào)告顯示本設(shè)計(jì)共消耗了679個(gè)LE資源。調(diào)用Modelsim軟件仿真驗(yàn)證。使用了Quartus II軟件的Signaltap邏輯分析儀,捕捉了讀寫(xiě)器實(shí)際工作時(shí)FPGA的編解碼數(shù)據(jù)。

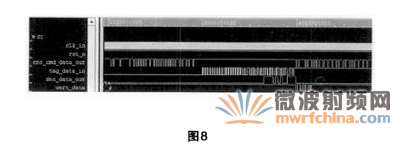

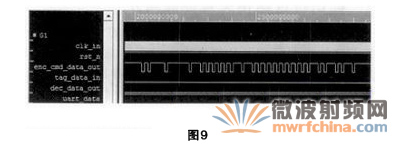

圖8是讀寫(xiě)器先后發(fā)送不同命令并與標(biāo)簽交互的部分流程。圖9是讀寫(xiě)器發(fā)送的Query命令的PIE編碼,所發(fā)送的命令數(shù)據(jù)是1000_00110000 0000010101,其中前4位1000為Query命令的命令碼,后面18位則為命令數(shù)據(jù)。

圖8 命令發(fā)送流程及標(biāo)簽信息的返回

圖9 命令的PIE編碼

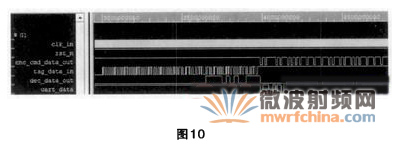

圖10是讀寫(xiě)器接收到標(biāo)簽返回的miller2編碼信息后的操作。為了便于觀察,將解碼后的數(shù)據(jù)也作為一路信號(hào)顯示,即decode_data。最后一路信號(hào)是串口要發(fā)送的數(shù)據(jù)。圖10中的enc_cmd_data_out信號(hào)是讀寫(xiě)器接收到標(biāo)簽返回來(lái)的信息后,發(fā)出的ACK命令,發(fā)送的命令數(shù)據(jù)為01_0001111010100111,其中前兩位01為ACK命令的命令碼,后面的16位數(shù)據(jù)按照協(xié)議要求為標(biāo)簽返回的RN16。

圖10 命令的miller2解碼

圖11 Signaltap的采樣信號(hào)

圖11是在讀寫(xiě)器工作時(shí)利用Signaltap邏輯分析儀捕獲到的解碼后的標(biāo)簽數(shù)據(jù)及采樣信號(hào)。

結(jié)語(yǔ)

本文介紹了在EPCC1G2協(xié)議下,利用FPGA快速處理大量數(shù)據(jù)流的優(yōu)勢(shì),實(shí)現(xiàn)UHF RFID讀寫(xiě)器中編解碼模塊的設(shè)計(jì)方案,解決了讀寫(xiě)器讀取標(biāo)簽速率難以提升的問(wèn)題。經(jīng)過(guò)軟件仿真與實(shí)際硬件測(cè)試,讀寫(xiě)器工作良好,速度、性能均得到顯著提升。

來(lái)源:電子科技大學(xué)作者:于志宏,張紅雨

粵公網(wǎng)安備 44030902003195號(hào)

粵公網(wǎng)安備 44030902003195號(hào)