《射頻微波芯片設計》專欄適用于具備一定微波基礎知識的高校學生、在職射頻工程師、高校研究所研究人員,通過本系列文章掌握射頻到毫米波的芯片設計流程,設計方法,設計要點以及最新的射頻/毫米波前端芯片工程實現技術。

本文共分為三個部分:電源端加旁路電容的作用、旁路電路的高頻特性以及電源旁路電容的選擇。(全文閱讀大概需4分鐘,希望博主敝帚自珍的這點理解對你有一點點幫助,當然文中的觀點和陳述也可能不正確,歡迎交流討論)

前言

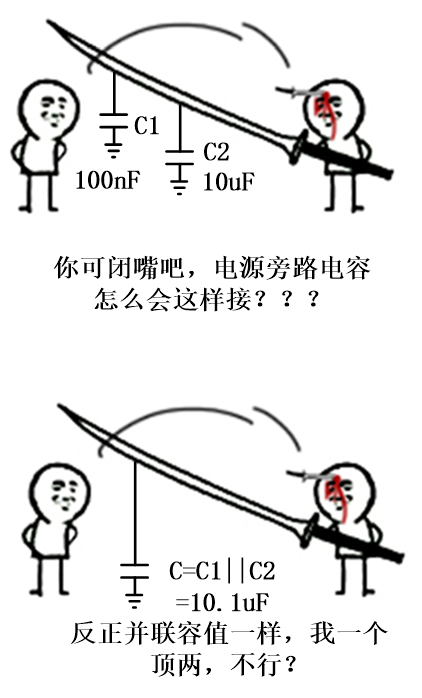

可能大伙兒看到“電源旁路電容為何要選擇0.1uF 10uF?”這個標題,已經準備好50米大砍刀,擼起了袖子準備開噴啦

對于電容這個名詞,相信咋門做電路的朋友(或者說學過模電,電路分析的童鞋們)再熟悉不過了,其或為隔直通交,或為匹配,或為旁路,或為傳感器,或為DAC全二進制權重的電容陣列等等,基本上在有源電路與系統中99.99%的概率都會用到電容。

在微波射頻網《3D動畫+動圖|詳解電容工作原理》一文中,詳細展開了關于電容的一些原理和基本用法,大家感興趣可以前去進一步學習。本文主要集中討論下射頻微波電路中的電源去耦旁路電容的使用,根據筆者的理解去討論回答下面兩個問題:

(1)在射頻電路中,為什么電源需要加旁路電容?

(2) 針對射頻電源端的旁路電容我們又該如何選擇呢,是不是直接用常見到的0.1uF,10uF的組合就可以了呢?

電源端加旁路電容的作用

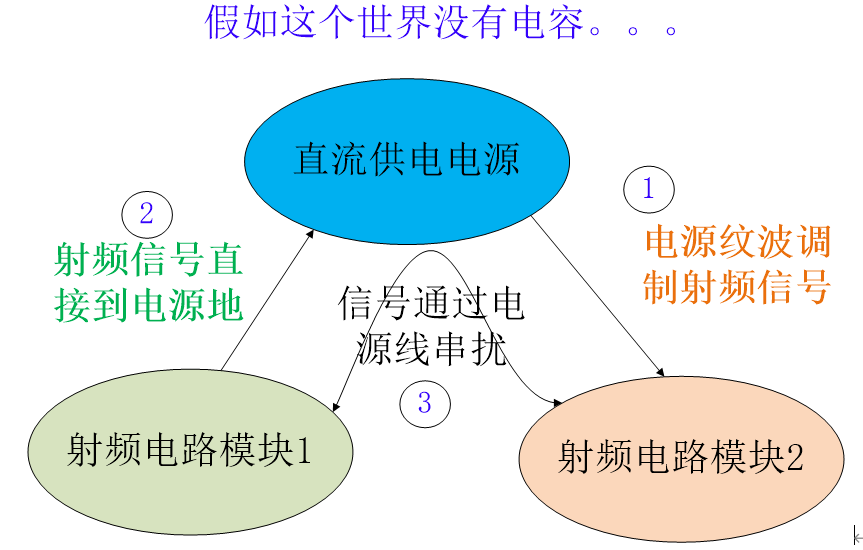

我們知道,射頻電路最終需要外部提供一個直流電源供電,這個直流電源與射頻芯片內部的晶體管或者場效應管的基極(柵極)或者集電極(漏極)直接相連,一方面,由于電源具有一定的紋波,往往會導致射頻信號受到調制,表現出一定的信號惡化,更有甚者導致電路不穩定;另一方面,電路里面的射頻信號看到電源端的等效輸入阻抗極小,這便導致射頻信號直接傳輸到了電源的地端,是輸出射頻信號大打折扣;最后便是各個模塊之間,通過電源線相互耦合,導致射頻模塊電路性能惡化。

相信做過電路的童鞋們一定閱讀過由日本鈴木雅臣寫的《晶體管電路設計(上)(下)》一書,該書可為學做實際模擬電路的寶典,在書中有這么一段話,我這里給摘抄下來。

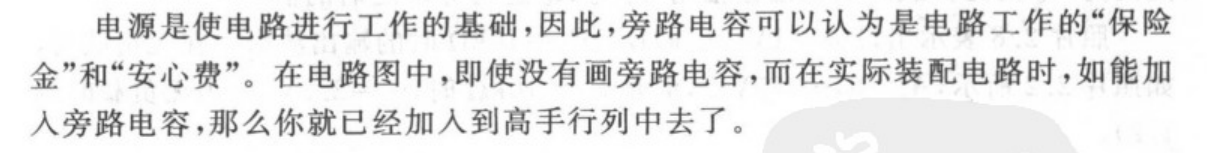

因此在電源端加載旁路電容,不管是在模擬電路還是數字電路,都是十分必要的。

旁路電容的高頻特性

既然在電源端加載旁路電容十分必要,那么我們設計的時候怎么加載,加載多少旁路電容合適呢???

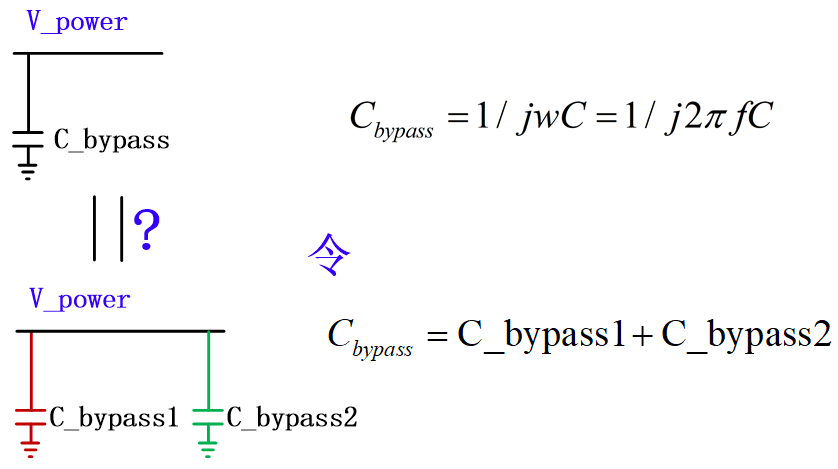

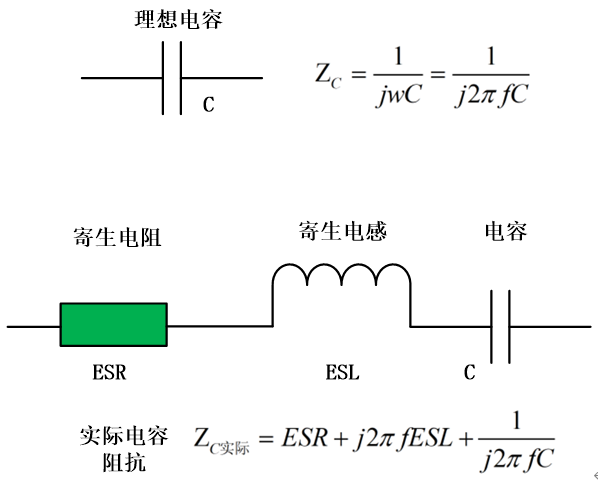

首先,我們知道電容的阻抗公式為:

那么在實際電路中,我們往往采用的多個旁路電容,這個時候一些小機靈就會問,豈不是就可以用一個來代替了?

咋一看上面的等效電路沒毛病,至少從數學層面上來看似乎無懈可擊,那么我們是不是就可以直接用一個電容值與兩個并聯電容值相同的電容來等效兩個并聯了呢?

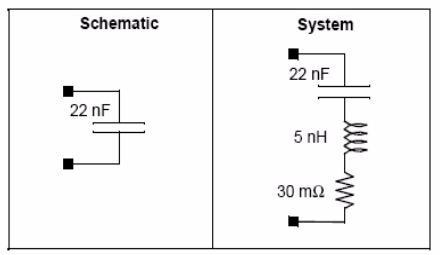

從物理層面上來看,實際的電容是由寄生電阻,寄生電感,電容串聯而成,如下圖所示

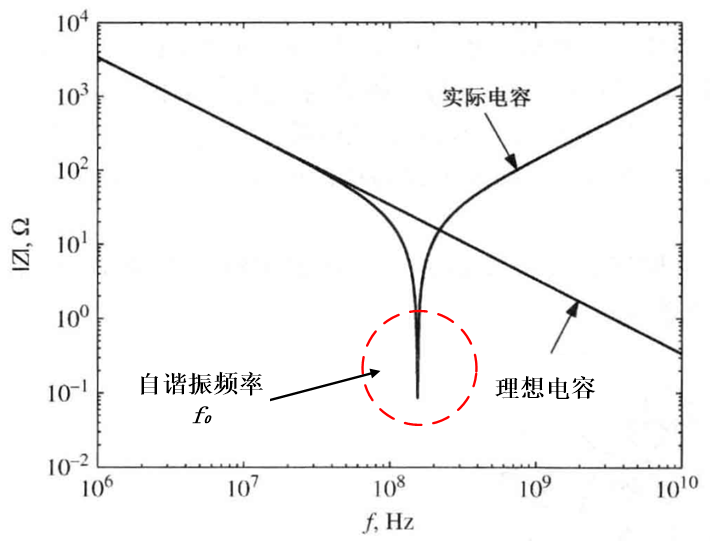

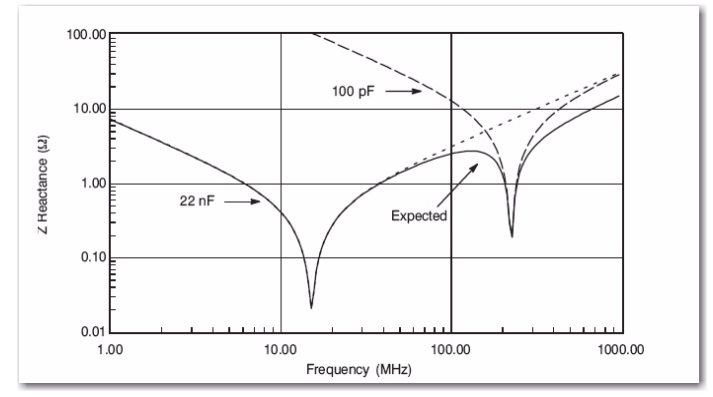

因此我們可以得到如下所示的電容的頻率響應函數曲線,當電容工作在自諧振頻率時,電容的阻抗為純實部,低于自諧振頻率時呈現容性,高于自諧振頻率時,電容變成了電感變現為感性。

因此,如果我們如果只是在電源上只加載一個電容,勢必只能在比較窄的帶寬內可以實現良好的旁路濾波效果(在一定帶寬內對射頻信號呈低阻狀態),正如《晶體管電路設計》一書中講到,由于電容的寄生效應,為了得到寬帶內旁路濾波效果,我們一般至少需要加兩個容值有差異的電容并聯到電源線。

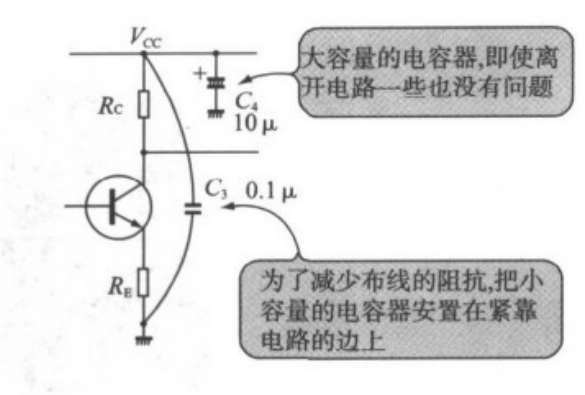

然而,同樣在鈴木雅臣的《晶體管電路設計》一書中并沒有給出這兩個容值一般差多少,書中倒是給出了一個實例,截圖如下所示:

書中的電源旁路電容,選擇了10uF和0.1uF,這樣兩個電容的容值比達到了100:1,這個時候,這樣的示例在實際使用時往往又會存在一些問題,那到底是什么問題呢,我們下一小部分再來討論。

電源旁路電容的選擇

承接上一小節的問題,我們討論到了,旁路電容的比值問題,如果兩電容差值過大會惹來一些不必要的麻煩,那么到底是啥麻煩呢???”。

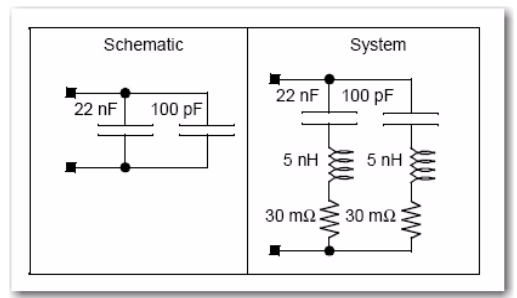

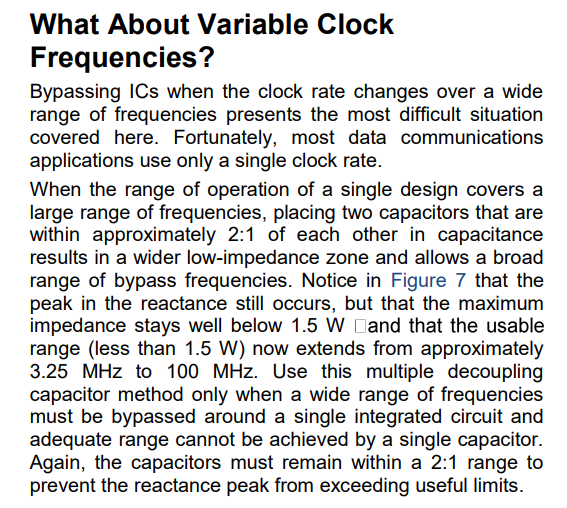

首先我們先看一個由英飛凌公司給出的一個數據手冊《Infineon-AN1032_Using_Decoupling_Capacitors-ApplicationNotes-v05_00-EN》,英飛凌想必大家都熟悉吧,全球功率半導體市場的市占率約為19%,排名第一,2020年4月,英飛凌以90億歐元成功收購美國同行賽普拉斯(Cypress),讓其實力更是傲視群雄。那么其官網給出的關于旁路去耦電容的相關數據手冊想必對我們還是有一定幫助的,在文中其提到了22nF電容和100pF的等效電路如下圖所示:。

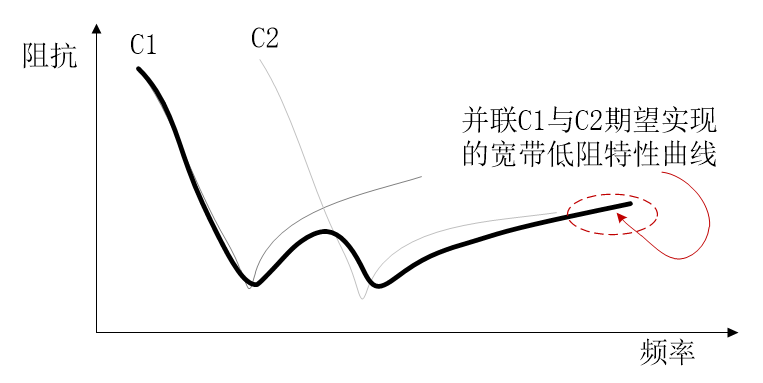

我們期望當22nF的電容和100pF的電容并聯后得到如下實線所示的效果:

然而現實是當22nF的電容和100pF的電容并聯后,得了到如下實線所示的效果:

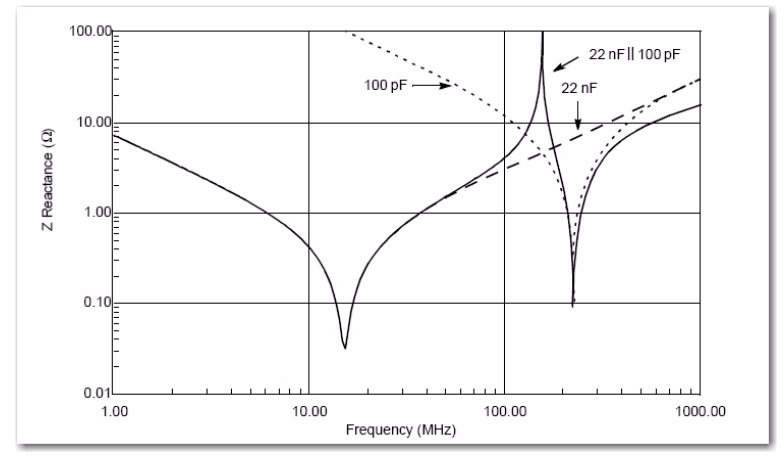

所以殘酷的現實告訴我們,原本并聯兩個電容是想得到一個阻抗相對較低的,寬帶的平滑曲線,但是現實是打臉的,在并聯完了22nF與100pF的電容后,在其原來的兩個電容的阻抗曲線交疊處出現了一個阻值極大值諧振點,這也導致這樣組合并不合適于電源濾除高頻的一些信號到地。

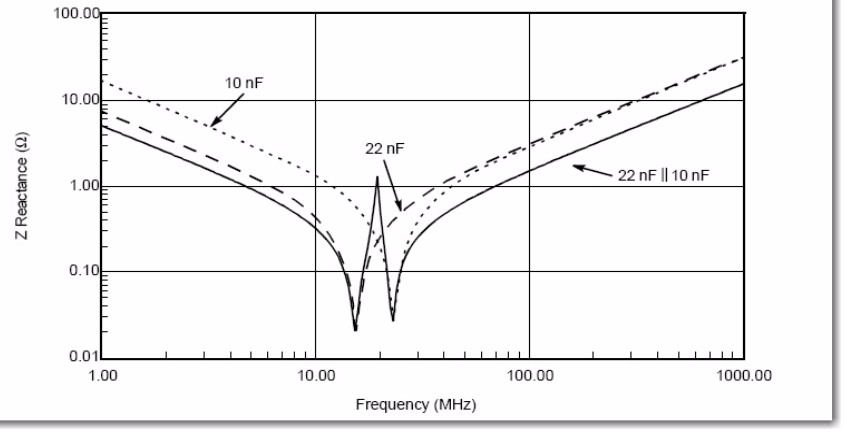

那么該如何選擇旁路電容值呢?且看手冊中的說明,如下

也就是說,我們最好采用的旁路電容值的間隔不要太遠,最好是能夠把容值之比控制在2:1之內。有圖有真相,下面給出手冊中將原來的20nF與100pF并聯,改成20nF和10nF電容并聯后的的阻抗-頻率響應曲線圖:

因此,后面如果要做好電路電源的濾波,旁路電容的選擇要慎重又慎重,特別是看過上一篇射頻問問RF測試專欄里面由J博客主寫作的《PA的包絡跟蹤電源》一文,也提到了在功率放大器設計的時候,去耦和濾波一定要小心考慮。

好了,看到這里大伙心中是不是對電源旁路電容的使用原則有點點感覺了,

似乎明白的點在于:

1. 對電源加載旁路電容,由于寄生效應,我們常常采用兩個以上的并聯電容,用以提高其工作帶寬;

2. 兩個電容的電容比盡量控制在2:1。

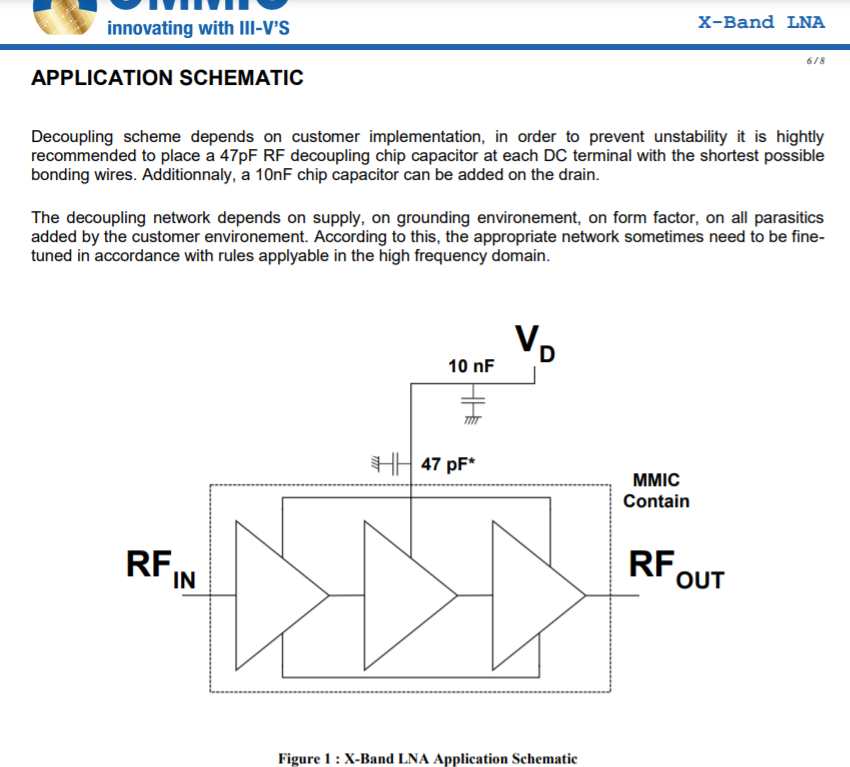

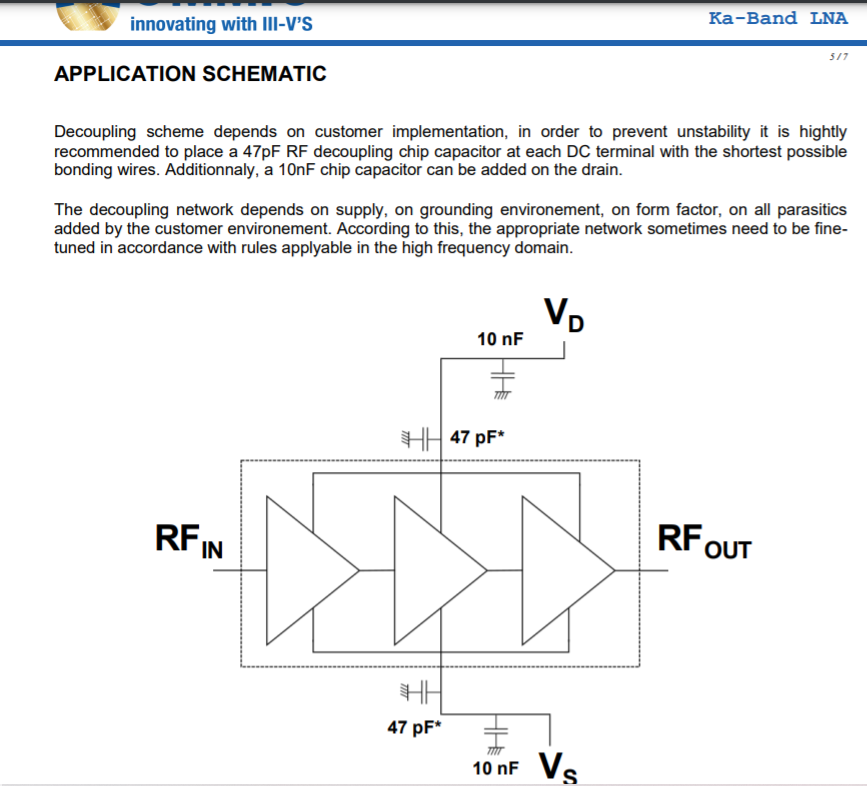

這個時候,我們隨便打開一些射頻微波芯片數據手冊,我看一些微波毫米波數據手冊上面給的芯片外圍參考旁路電容并非我們所述的2:1的比例,比如這樣的:

(某Ka波段LNA旁路電容選取值推薦)

(某W波段LNA旁路電容選取值推薦)

這個時候手機旁邊的你是不是又犯難了,這個旁路電容到底該咋選取啊!!!

好了,筆者這里給出一些自家敝帚般的觀點,如果說得不對的地方,歡迎留言或者到群里來和大家一起交流探討

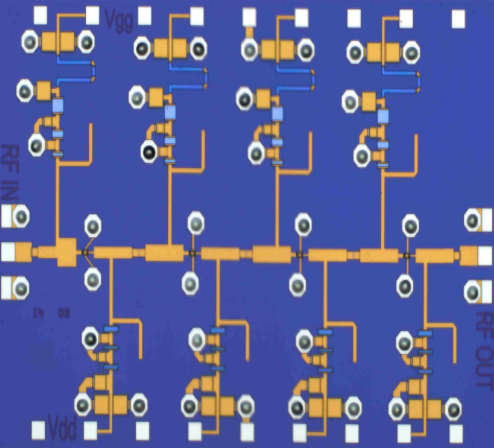

1. 針對板級射頻電路的電源旁路電容的選擇與布局

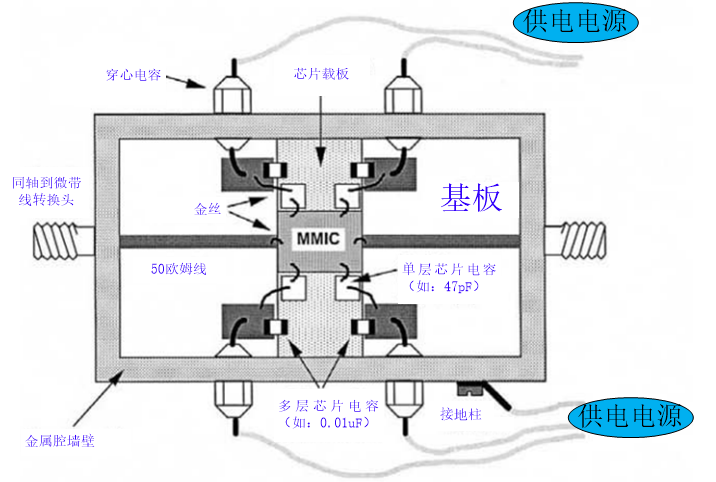

小電容盡量靠近芯片,大小電容的值最好是按照芯片數據手冊的推薦值來,如下圖示例所示:

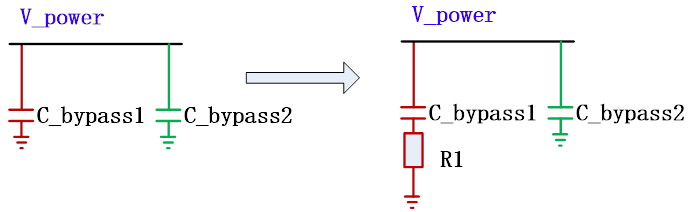

如果按照數據手冊的旁路測試得到的電路在低頻仍有振蕩,不妨考慮在小電容C_baypass1上面串聯一個小電阻R1,比如下圖所示:

在上文所述的英飛凌的那個數據手冊之所以會存在并聯后的一個諧振尖峰的原因,主要是兩個電容的響應曲線交疊處的各自的電阻都比較大。因此,如果我們在旁路電容中的某一個低寄生電阻的那個小電容上面串聯一個小電阻,那么整個電源的旁路針對某一頻率的等效電阻就會與最小的那個電阻值接近,當我們人為地設計一個小電阻后,便可以盡量規避掉諧振尖峰阻抗。

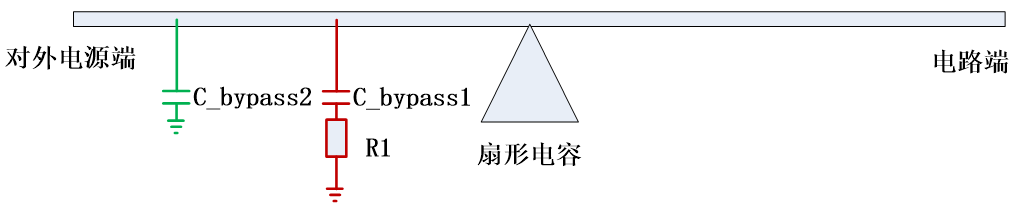

2.針對芯片級射頻電路的電源旁路電容的選擇與布局

芯片級的旁路電容,主要還是需要注意電容自諧振頻率的位置,盡可能地把最小的電容的自諧振頻率推到工作頻率以外,同樣如果仍舊無法解決低頻諧振,可以嘗試上文提到的方案,得到如下圖所示的電源旁路電路結構:

當然,第一級扇形電容還可以用多層傳輸線包夾射頻地的平板形式的電容代替,或許大伙還有更多想法和技巧,歡迎留言或者入群交流。

本期內容就到這里,希望沒有浪費大家伙的時間,能有所獲。

作者:RFIC_拋磚?

粵公網安備 44030902003195號

粵公網安備 44030902003195號