幾乎每個(gè)RF和微波系統(tǒng)都需要頻率合成器。頻率合成器產(chǎn)生本振信號(hào)以驅(qū)動(dòng)混頻器、調(diào)制器、解調(diào)器及其他許多RF和微波器件。頻率合成器常被視為系統(tǒng)的心跳,創(chuàng)建方法之一是使用鎖相環(huán)(PLL)頻率合成器。

傳統(tǒng)上,一個(gè)簡(jiǎn)單的PLL將壓控振蕩器(VCO)輸出頻率分頻,將其與一個(gè)參考信號(hào)進(jìn)行比較,然后微調(diào)VCO控制電壓以微調(diào)其輸出頻率。很多年來,PLL和VCO是兩種單獨(dú)的芯片——這就是分立解決方案。VCO產(chǎn)生實(shí)際輸出信號(hào);PLL監(jiān)控輸出信號(hào)并調(diào)諧VCO,以將其相對(duì)一個(gè)已知參考信號(hào)鎖定。

分立解決方案有多個(gè)優(yōu)點(diǎn):

· 可設(shè)計(jì)每個(gè)分立芯片以提供盡可能好的性能。· PLL和VCO之間的物理距離降低了交叉耦合效應(yīng),使輸出端的干擾雜散信號(hào)最小化。

· 如果環(huán)路中的一個(gè)芯片損壞,只需更換較少的元件。

分立解決方案在頻率合成器行業(yè)長(zhǎng)期處于優(yōu)勢(shì)地位,但它也有缺點(diǎn)。一個(gè)主要問題是:為了容納兩個(gè)芯片及其所有支持元件,分立解決方案需要大量板空間。這導(dǎo)致終端產(chǎn)品尺寸較大且成本較高。

分立解決方案的另一個(gè)主要問題是傳統(tǒng)VCO的輸出頻率范圍較窄。典型VCO帶寬為50 MHz至500 MHz;雖然可以達(dá)到2 GHz左右,但這需要基于運(yùn)算放大器的有源濾波器。對(duì)任何希望實(shí)現(xiàn)更寬頻率范圍的人來說,這都是一個(gè)重大挑戰(zhàn)。為了創(chuàng)建頻率范圍更寬的合成器,需要多個(gè)PLL、VCO、支持元件、濾波、開關(guān)和電源!這會(huì)使設(shè)計(jì)的板空間和成本呈指數(shù)式增加。分立解決方案不僅會(huì)影響板設(shè)計(jì),而且涉及大量額外工作,包括為每種器件進(jìn)行質(zhì)量評(píng)定、開發(fā)軟件及庫存管理。

大約10年前,基于PLL的頻率合成器行業(yè)有了一次突破。第一代集成式PLL和VCO(PLL/VCO)開始出現(xiàn)在市場(chǎng)上。這一重大發(fā)展意味著電路板可以更小,成本可以更低,額外工作可以大幅減少。集成解決方案還意味著VCO架構(gòu)可以改變,利用一個(gè)器件便能實(shí)現(xiàn)寬帶頻率合成器。我們將探討VCO架構(gòu),以及向集成VCO的轉(zhuǎn)變?nèi)绾伍_啟高性能頻率合成器的大門。

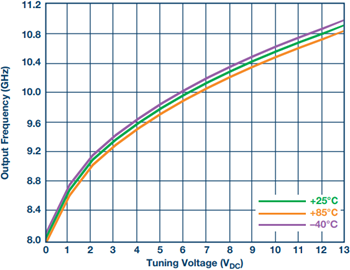

傳統(tǒng)VCO是很簡(jiǎn)單的器件——電壓施加于VCO的調(diào)諧引腳,隨即輸出某一頻率;電壓提高,輸出頻率也提高;電壓降低,輸出頻率也降低。圖1所示為GaAs MMIC VCO的調(diào)諧電壓與輸出頻率的關(guān)系示例——13 V調(diào)諧范圍需要有源濾波器或帶高壓電荷泵的PLL。

圖1. 傳統(tǒng)VCO——調(diào)諧電壓與輸出頻率的關(guān)系

集成PLL/VCO解決方案采用的VCO架構(gòu)雖然是基于傳統(tǒng)架構(gòu),但有很大的不同。集成PLL/VCO將多個(gè)傳統(tǒng)VCO集成在一起,產(chǎn)生一個(gè)帶寬非常寬的VCO。各個(gè)VCO——通過接入和斷開電容而創(chuàng)建——稱為頻段。PLL和VCO集成在一個(gè)芯片上,因而可實(shí)現(xiàn)多頻段架構(gòu)。每次用戶希望鎖定一個(gè)新頻率時(shí),器件就會(huì)啟動(dòng)VCO校準(zhǔn)過程,芯片快速遍歷VCO頻段,選擇一個(gè)最適合所需輸出頻率的頻段。一旦選定VCO頻段,PLL就會(huì)鎖定環(huán)路,使輸出保持在所需頻率。

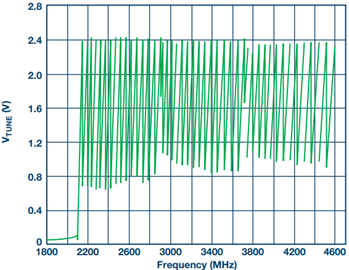

第一代PLL/VCO芯片就有超過4 GHz的帶寬!相比之下,分立解決方案只有100 MHz到300 MHz帶寬——而且4 GHz頻率范圍是由一個(gè)微小芯片實(shí)現(xiàn)的,而不是之前需要的多個(gè)PLL、VCO、濾波器和開關(guān)。圖2所示為一個(gè)多頻段PLL/VCO的調(diào)諧電壓與輸出頻率的關(guān)系。本例中,基頻VCO輸出范圍規(guī)定為2200 MHz至4400 MHz。VCO輸出之后有一組分頻器,不過其仍在芯片內(nèi)部,可將信號(hào)分頻至最低35 MHz;超過4 GHz帶寬就是這樣得到的——全部來自單個(gè)5 mm × 5 mm封裝。

圖2. 多頻段VCO——調(diào)諧電壓與輸出頻率的關(guān)系

雖然這一突破性技術(shù)大大提高了頻率范圍,減少了板空間、成本和額外工作,但它仍有缺點(diǎn),使得集成解決方案不能完全取代分立解決方案。許多應(yīng)用的最重要性能規(guī)格(除了頻率范圍)是相位噪聲。

相位噪聲為何如此重要?想象一個(gè)信號(hào)通過晴朗空氣傳輸?shù)南到y(tǒng)。假設(shè)在發(fā)射天線處發(fā)射信號(hào)的信噪比為50 dB。這意味著,接收機(jī)要接收的信號(hào)比發(fā)射信號(hào)任一側(cè)的噪聲(即鄰近的更高和更低頻率)要強(qiáng)50 dB。假定此信號(hào)可以傳輸10英里,這之后的信號(hào)功率將衰變?yōu)樵肼暎瑐鬏攲G失。現(xiàn)在,假設(shè)頻率合成器的相位噪聲改善了3 dB。這意味著發(fā)射信號(hào)的信噪比為53 dB。因此,發(fā)射信號(hào)功率是先前10英里距離信號(hào)的兩倍,它在衰變?yōu)樵肼曋澳軌騻鬏數(shù)酶h(yuǎn)。更遠(yuǎn)的傳輸距離意味著所需的中繼器/發(fā)射器會(huì)更少,成本得以降低。

除了這個(gè)通信例子以外,還有來自電子測(cè)試與測(cè)量領(lǐng)域?qū)ο辔辉肼曅阅艿耐苿?dòng)。無論通信行業(yè)需要什么樣的相位噪聲性能,電子測(cè)試與測(cè)量?jī)x器需要的相位噪聲性能只會(huì)更高,只有這樣才能測(cè)量通信協(xié)議。

雖然許多解決方案能從分立式轉(zhuǎn)移到集成式——節(jié)省數(shù)以百萬計(jì)美元的工藝成本——但第一代PLL/VCO的相位噪聲性能還不夠好,不適合許多要求低相位噪聲的應(yīng)用。除相位噪聲性能外,與很多需要分立PLL和VCO的應(yīng)用相比,頻率范圍也相當(dāng)?shù)汀?/p>

頻率范圍問題可通過倍頻器和乘法器解決,但這些是高功耗器件,而且會(huì)增加解決方案的成本和板空間。

幸運(yùn)的是,在推出這些集成解決方案的同時(shí),業(yè)界便已著手開發(fā)新的IC工藝以獲得人們強(qiáng)烈期盼的相位噪聲和頻率范圍改善。

此時(shí)的舞臺(tái)已為第二代集成PLL/VCO的亮相做好準(zhǔn)備。第二代產(chǎn)品的要求如下:

· 輸出頻率大于4.4 GHz。· 相位噪聲性能可與分立解決方案相比擬。

· 在單個(gè)小封裝中集成PLL和VCO。

· 成本低于分立解決方案。

2014年晚些時(shí)候,第二代集成PLL/VCO正式登場(chǎng)。市場(chǎng)上開始出現(xiàn)超過10 GHz輸出頻率范圍的產(chǎn)品,其相位噪聲堪比分立VCO,采用5 mm ×5 mm封裝,價(jià)格低于類似的分立PLL和VCO解決方案(但其頻率范圍要窄得多)。

例如,ADI公司的ADF4355系列實(shí)現(xiàn)了第二代的所有要求:

· 輸出頻率從50 MHz到13.6 GHz (一個(gè)端口≤6.8 GHz,另一個(gè)端口≤6.8 GHz)。· 相位噪聲:

○ 傳統(tǒng)分立VCO在10 GHz時(shí):–110 dBc/Hz (100 kHz偏移)和–135 dBc/Hz (1 MHz偏移)。分立VCO用頻率范圍換取相位噪聲性能。

○ ADF4355系列在10 GHz時(shí):–106.5 dBc/Hz (100 kHz偏移)和–130 dBc/Hz (1 MHz偏移)。

· 5 mm ×5 mm LFCSP封裝。

· 價(jià)格隨器件而異,但成本低于分立解決方案。

現(xiàn)在,用戶不僅可享有分立解決方案的相位噪聲性能好處,還能獲得集成解決方案的所有其他好處。更有利的是,PLL技術(shù)在這些年中也得到了發(fā)展,因此,第二代PLL/VCO器件的PLL性能也有很多改善。

對(duì)于第一代PLL/VCO,PLL模塊的最大鑒頻鑒相器(PFD)頻率在32 MHz左右,小數(shù)N分頻器的分辨率在12位左右。這種組合意味著典型通道分辨率在數(shù)十kHz。第二代PLL/VCO的最大PFD頻率大于100 MHz,小數(shù)N分頻器的分辨率為25位,甚至高達(dá)49位。這主要有兩個(gè)好處——PFD頻率越高,PLL相位噪聲就越低(PFD頻率每提高一倍,N分頻器便可減半,N分頻器噪聲分布相應(yīng)地降低3 dB);25位甚至更高的分辨率支持精密頻率生成和亞Hz頻率步進(jìn)(頻率分辨率)。

雜散性能

集成PLL/VCO有一個(gè)重要方面需要討論。上文指出了分立解決方案的一個(gè)優(yōu)點(diǎn),那就是兩個(gè)芯片之間的物理隔離降低了PLL與VCO之間的交叉耦合,從而降低了干擾雜散信號(hào)的功率。當(dāng)集成PLL和VCO時(shí),雜散性能不可避免會(huì)下降。市場(chǎng)上的某些器件設(shè)法將此性能下降保持在非常低的水平,使PLL/VCO具有令人吃驚的良好雜散性能——HMC830就是一例。其他PLL/VCO器件需要采取一些額外措施來改善雜散水平,以便支持某些高性能產(chǎn)品。

改變PFD頻率以消除整數(shù)邊界雜散

一種技術(shù)是利用頻率規(guī)劃算法改變PLL的PFD頻率。這樣可以將PFD模塊引起的雜散信號(hào)轉(zhuǎn)移到不會(huì)造成較大影響的區(qū)域,從而在事實(shí)上消除雜散。相關(guān)詳細(xì)信息請(qǐng)參閱“分析、優(yōu)化和消除集成VCO的鎖相環(huán)在高達(dá)13.6 GHz處的整數(shù)邊界雜散”一文。

隔離PLL和VCO

如上所述,PLL和VCO電路緊密靠近可能引起不需要的耦合。為解決這一問題,可使用雙芯片解決方案將PLL和VCO電路從物理上隔離開來。這樣既能獲得分立解決方案的低雜散信號(hào)優(yōu)勢(shì),又能享有集成解決方案的寬輸出頻率優(yōu)勢(shì)。

ADI公司分立小數(shù)N分頻PLL產(chǎn)品系列中的HMC704非常適合這一任務(wù)。在這種解決方案中,VCO輸出信號(hào)之一(ADF4355系列全部都有兩路輸出)饋送到HMC704(對(duì)此信號(hào)使用可選的10 dB衰減器可進(jìn)一步降低雜散水平)。ADF4355 PLL最初用于完成VCO校準(zhǔn)并鎖定所需頻率。然后可關(guān)閉ADF4355 PLL部分,即讓電荷泵處于三態(tài)并使計(jì)數(shù)器保持復(fù)位狀態(tài),從而消除PLL中的所有雜散,而HMC704將使環(huán)路保持鎖定。這樣做有多方面好處:

· 使用非VCO所在芯片中的PLL可降低雜散功率。· HMC704的固有雜散性能優(yōu)于ADF4355 PLL——因此,雜散進(jìn)一步降低。

· HMC704的歸一化相位噪底低于ADF4355 PLL——因此,頻率合成器輸出端的噪聲更低。

為使環(huán)路閉合,HMC704電荷泵輸出連接到一個(gè)環(huán)路濾波器。環(huán)路濾波器輸出必須連接到ADF4355 VTUNE引腳。當(dāng)環(huán)路鎖定時(shí),HMC704僅用作PLL,ADF5355僅用作VCO。要完全消除ADF4355 PLL中的雜散,當(dāng)ADF4355 PLL不使用時(shí),必須將ADF4355參考輸入引腳接地。幸運(yùn)的是,這在HMC704中很容易做到。HMC704有一個(gè)通用輸出(GPO)引腳——此引腳可直接連到ADF4355參考輸入引腳。當(dāng)ADF4355需要參考信號(hào)時(shí)(用于VCO校準(zhǔn)),HMC704可將其參考信號(hào)路由到GPO引腳;當(dāng)沒必要將ADF4355參考輸入引腳接地時(shí),可設(shè)置HMC704通過GPO引腳輸出GND。圖3顯示的便是這種電路。

圖3.利用外部HMC704 PLL鎖定ADF4355以改善雜散性能

ADI公司推出了四款具有第二代PLL/VCO性能的重要器件——ADF4355系列。該系列有四款器件:其中三款非常相似,僅頻率范圍不同;第四款是低功耗版本。

· ADF4355-2:集成式PLL/VCO,輸出53 MHz至4400 MHz。· ADF4355:集成式PLL/VCO,輸出53 MHz至6800 MHz。

· ADF5355:集成式PLL/VCO,輸出53 MHz至13,600 MHz。

· ADF4355-3:低功耗集成式PLL/VCO,輸出51 MHz至6600 MHz。

所有器件信息均可在analog.com 上找到,包括數(shù)據(jù)手冊(cè)、樣片、評(píng)估板、控制軟件、仿真軟件、用戶指南、EngineerZone®在線支持社區(qū)等。

粵公網(wǎng)安備 44030902003195號(hào)

粵公網(wǎng)安備 44030902003195號(hào)