十幾年前,頻率控制行業(yè)推出了基于鎖相環(huán)(PLL)的振蕩器,這是一項(xiàng)開拓性創(chuàng)新技術(shù),采用了傳統(tǒng)晶體振蕩器(XO)所沒有的多項(xiàng)特性。憑借內(nèi)部時(shí)鐘合成器IC技術(shù),基于PLL的XO可編程來支持更寬廣的頻率范圍。這一突破消除了為在特定頻率實(shí)現(xiàn)共振而切割和加工石英所需的材料加工工藝步驟。這一創(chuàng)新也使得對(duì)基于PLL的XO進(jìn)行頻率編程成為可能并且實(shí)現(xiàn)極短交貨周期。

鑒于傳統(tǒng)振蕩器交貨周期可能接近14周或更長(zhǎng),許多硬件設(shè)計(jì)人員渴望利用可編程振蕩器獲得顯著的交貨周期優(yōu)勢(shì)。不幸的是,嚴(yán)重的問題發(fā)生了。一些已經(jīng)從傳統(tǒng)XO遷移到基于PLL的XO的設(shè)計(jì)陷入了關(guān)聯(lián)抖動(dòng)(jitter-related)問題之中,這會(huì)引起關(guān)聯(lián)應(yīng)用(application-related)失效,涉及范圍從通信鏈路中的超高位錯(cuò)誤率到無法工作的SoC和處理器。這些問題迫使許多IC供應(yīng)商規(guī)定:基于PLL的振蕩器不能和他們的器件配合使用。這種形勢(shì)的變化使得想通過基于PLL的振蕩器獲得頻率靈活性和短交付周期優(yōu)勢(shì)的硬件工程師面臨挑戰(zhàn)。

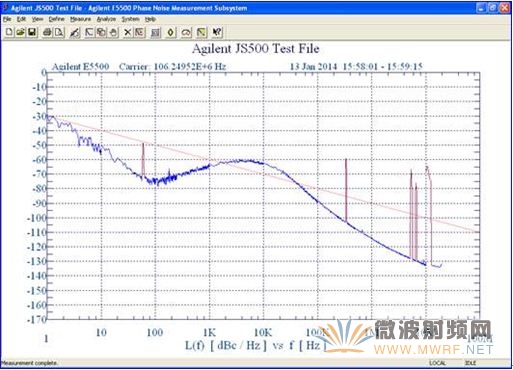

為什么會(huì)出現(xiàn)這種情況?其原因在于來自不同供應(yīng)商的PLL技術(shù)差異極大。不合格的PLL設(shè)計(jì)導(dǎo)致過多的振蕩器相位噪聲和抖動(dòng)峰值,如圖1中左側(cè)畫面所示。這個(gè)特定的基于PLL的XO在12kHz-20MHz帶寬上的相位抖動(dòng)為150ps RMS。這種性能水平使它不適合為高速PHY提供時(shí)鐘,高速PHY通常需要<1ps RMS 抖動(dòng)的參考時(shí)鐘。XO的周期抖動(dòng)在圖1右側(cè)圖片中有顯示。這種雙峰周期抖動(dòng)可能是一個(gè)出現(xiàn)PLL穩(wěn)定性問題的信號(hào),PLL穩(wěn)定性能夠?qū)κ褂眠@個(gè)XO的SoC產(chǎn)生有害的性能影響。與可編程振蕩器展現(xiàn)抖動(dòng)峰值有關(guān)的第二個(gè)領(lǐng)域是級(jí)聯(lián)PLL。當(dāng)這樣一個(gè)基于PLL的振蕩器被連接到一個(gè)后續(xù)電路中帶有PLL的IC上時(shí),抖動(dòng)可能會(huì)增加。

圖1–不合格的基于PLL的XO設(shè)計(jì)導(dǎo)致過多的相位噪聲和周期抖動(dòng)

好消息是并非所有的PLL,確切的說不是所有基于PLL的振蕩器,都是一樣的。通過特有的PLL設(shè)計(jì)技術(shù),可編程振蕩器能夠提供可媲美一流石英振蕩器的抖動(dòng)性能,同時(shí)克服級(jí)聯(lián)PLL帶來的問題。這些高性能的基于PLL的振蕩器能夠用于處理器/SoC時(shí)鐘,以及高速串行器、PHY和FPGA時(shí)鐘。

開發(fā)人員可以使用三個(gè)簡(jiǎn)單的標(biāo)準(zhǔn)來評(píng)價(jià)基于PLL的XO能否被用于給定的應(yīng)用。

抖動(dòng)生成—在級(jí)聯(lián)的PLL應(yīng)用(例如FPGA和PHY時(shí)鐘),XO參考時(shí)鐘抖動(dòng)與FPGA/PHY內(nèi)部PLL抖動(dòng)相混合。采用低抖動(dòng)XO參考時(shí)鐘(例如<<1ps RMS相位抖動(dòng))可以最大化可容許的FPGA/PHY內(nèi)部PLL所產(chǎn)生的抖動(dòng)值,最大化整體設(shè)計(jì)的抖動(dòng)余量。

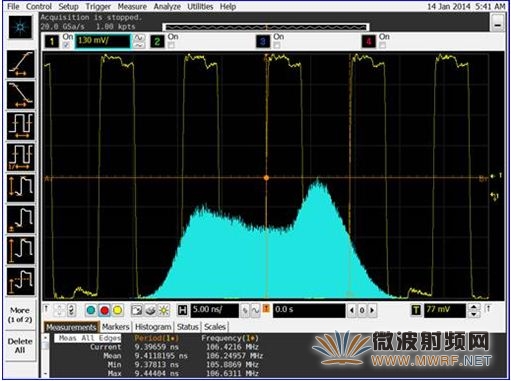

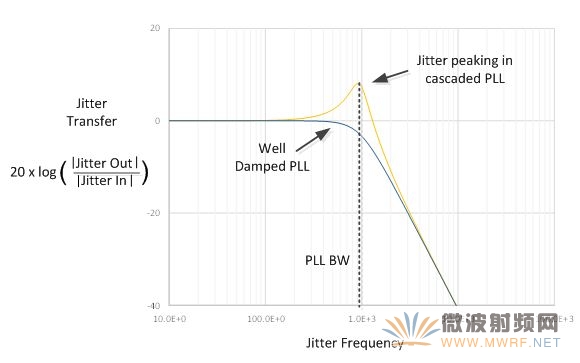

抖動(dòng)峰值—當(dāng)?shù)谝患?jí)和第二級(jí)PLL的環(huán)路帶寬相同時(shí),級(jí)聯(lián)PLL存在過大抖動(dòng)的風(fēng)險(xiǎn)。這種風(fēng)險(xiǎn)很容易通過使用一個(gè)具有相對(duì)較低內(nèi)部PLL帶寬的基于PLL的振蕩器進(jìn)行緩解。PLL應(yīng)當(dāng)?shù)玫胶芎玫囊种疲源_保不超過1%的峰值(<0.1db),如圖2所示。通用soc>1MHz。使用具有低抖動(dòng)峰值和極低內(nèi)部帶寬的基于PLL的振蕩器確保它的峰值不會(huì)與下游PLL的帶寬重疊。這種架構(gòu)使得第二級(jí)PLL容易的跟蹤第一級(jí)PLL的變化,同時(shí)維持可接受的環(huán)路穩(wěn)定性和相位余量。

圖2-基于PLL的抖動(dòng)跟蹤和過濾有助于減輕抖動(dòng)峰值

相位噪聲—怎樣才能知道基于PLL的振蕩器是否適合你的應(yīng)用呢?使用示波器較容易觀察振蕩器的周期抖動(dòng)。使用頻譜分析儀進(jìn)行振蕩器相位噪聲測(cè)量。如果你沒有頻譜分析儀,聯(lián)系你的頻率控制供應(yīng)商進(jìn)行相位噪聲測(cè)量。相位噪聲能夠通過應(yīng)用所需的相關(guān)抖動(dòng)合成帶寬,直接從相位噪聲圖表中計(jì)算出來。相位噪聲圖表也能顯示參考時(shí)鐘的雜散性能。疊加在相位抖動(dòng)上雜散信號(hào)能夠容易的進(jìn)行測(cè)量,以確保應(yīng)用需求得到滿足。相位噪聲圖表也顯示內(nèi)部PLL的任何峰值影響。過阻尼的PLL將展現(xiàn)出低峰值。

Silicon Labs提供了一個(gè)易于使用的在線抖動(dòng)計(jì)算器,能夠把相位噪聲轉(zhuǎn)換為抖動(dòng)。只需要簡(jiǎn)單的輸入載波頻率和與其相關(guān)的相位噪聲特征數(shù)據(jù),工具就能計(jì)算出時(shí)鐘的最終相位抖動(dòng)、周期抖動(dòng)和周期間抖動(dòng)。基于Web的工具在Silicon Labs網(wǎng)站即可獲得。

總之,當(dāng)今的可編程振蕩器提供了卓越的頻率靈活性、短期、可靠的交貨周期。然而,來自不同供應(yīng)商的可編程振蕩器所提供的PLL性能差異可能相當(dāng)大。對(duì)于包括FPGA收發(fā)器和以太網(wǎng)PHY時(shí)鐘在內(nèi)的高性能應(yīng)用來說,可編程振蕩器能夠容易的通過對(duì)比數(shù)據(jù)手冊(cè)規(guī)范中的抖動(dòng)參數(shù)進(jìn)行評(píng)估。

在由振蕩器驅(qū)動(dòng)的帶有內(nèi)部PLL的ASIC、SoC、FPGA或PHY應(yīng)用中,重要的是確保參考振蕩器和SoC的組合不要產(chǎn)生抖動(dòng)峰值。抖動(dòng)峰值通常不會(huì)列在振蕩器數(shù)據(jù)手冊(cè)中。一個(gè)簡(jiǎn)單的解決方法是進(jìn)行振蕩器的相位噪聲測(cè)量。這個(gè)相位噪聲分布將顯示對(duì)內(nèi)部PLL的任何峰值影響,并且能夠容易的轉(zhuǎn)換成等效的時(shí)鐘抖動(dòng)性能。

粵公網(wǎng)安備 44030902003195號(hào)

粵公網(wǎng)安備 44030902003195號(hào)