設計了一種低插入損耗、高隔離度的全集成超寬帶CMOS射頻收發開關芯片。該電路采用深N阱體懸浮技術,在1.8V電壓供電下,該射頻開關收發兩路在0.1-1.2GHz內的測試結果具有0.7dB的插入損耗、優于-20dB的回波損耗以及-37dB以下的隔離度。

目前,全球無線通信系統正處于快速發展進程中,無線通信“行業專網”系統也正處于飛速發展的黃金時期。我國無線通信行業專網所用頻點和帶寬種類繁多,其頻率 主要集中在0.1-1.2GHz。各專網使用不同的頻點、射頻帶寬和信號帶寬,標準不統一,導致各行業專網設備所用的射頻芯片不同,同時對各個窄帶射頻前 端芯片的需求難以形成規模效應,且成本高、配套困難。目前行業專網所用的窄帶射頻前端芯片多數被國外公司所壟斷,因此我們國家迫切的需要一套面向 0.1-1.2GHz行業專網頻段的無線寬帶射頻收發芯片,以滿足新一代寬帶無線移動通信網的基本需求。

射頻無線收發芯片已經在手機、 雷達、無線局域網(WLAN)及廣播等多個窄帶或寬帶無線收發系統中得到了廣泛應用。從頻域來看,超寬帶與傳統的窄帶和寬帶有著明顯的區別,超寬帶的相對 帶寬(信號帶寬與中心頻率之比)通常要在25%以上。此,0.1-1.2GHz頻段無線寬帶射頻收發芯片屬于超寬帶電路。目前,在CMOS工藝下,國 際、國內尚無成熟商用超寬帶射頻收發芯片解決方案可以滿足該頻段的設計需求。

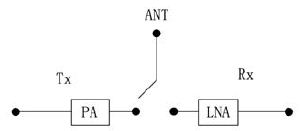

無線超寬帶射頻收發芯片由射頻收發開關(T/R Switch)、低噪聲放大器(LNA)、混頻器(Mixer)、功率放大器(PA)、濾波器等多個電路模塊組成。射頻收發開關(T/R switch)作為無線寬帶收發芯片的最前端電路,主要作用是控制整個收發機芯片的接收與發射狀態的切換(如圖1所示),它連接著收發天線、低噪聲放大器和 功率放大器,是收發芯片中的關鍵模塊。傳統射頻收發開關的制造工藝有很多,目前市場常見的產品絕大部分采用的是III-V族工藝或者PIN二極管等分立器 件。這類開關的優點是功耗較低,并且隔離度較好。然而它們的缺點是成本高、功耗大,并且占用面積也較大。隨著工藝技術的不斷發展,CMOS技術因其具有高 集成度、低成本和低功耗等突出優點,使得采用CMOS工藝實現射頻收發開關已經成為一種必然的趨勢。

圖1 射頻收發開關工作原理圖

插入損耗、隔離度和線性度,是衡量射頻收發開關特性的三個關鍵指標,除此之外,回波損耗也是一項主要指標。傳統的對稱式射頻收發開關普遍采用普通的四個 NMOS管串并聯結構進行設計。這種結構的優點是隔離度較好,但是一定程度上會惡化插入損耗和線性度,其典型仿真插入損耗為1dB左右。2008年,在基本的NMOS管串聯結構基礎上,采用深N阱工藝的NMOS器件,運用一種改進型的體懸浮(body-floating)技術,實現了 一個寬帶射頻收發開關。與傳統的串并聯結構開關電路相比,該結構具有更高的線性度以及更低的插入損耗等優點。

本文中所設計的 射頻收發開關是在典型的串并聯結構的電路基礎上,結合參考文獻中所述的襯底懸浮技術,實現了各項指標的良好折中。本文中的開關電路不僅具有較高的隔 離度特性,并且在線性度上也會有較大的改善。測試結果顯示,該射頻開關在0.1-1.2GHz頻段內實現了低于-37dB隔離度和0.7dB的插入損耗, 基于RFID 433MHz及GSM-R 900MHz典型應用頻段中,具有高于22dBm的1dB壓縮點。

1、方案設計

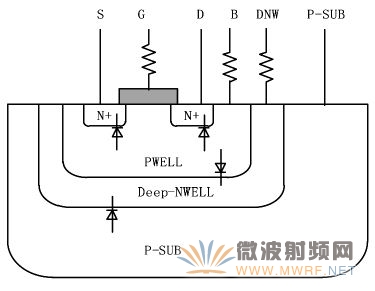

圖2(a)所示的為體懸浮技術所采用的深N阱工藝的NMOS器件截面圖。通常,開關線性度 的惡化原因是由于器件在工作狀態下瞬時導通的寄生二極管造成的。由于深N阱的存在,器件中會產生兩個額外的寄生二極管,分別為P阱/深N阱二極管和深N阱 /P型襯底二極管。因此,當P阱被一個大電阻懸空接地,同時深N阱接高電位后(如圖2(b)所示),所有的二極管都不會正向導通,不會產生閂鎖效應,從而 提高了整個電路的線性度。在本文的電路設計中,深N阱采用的是1.8V電壓偏置。

圖2 (a)深N阱NMOS晶體管截面圖

(b)NMOS管電阻連接說明圖

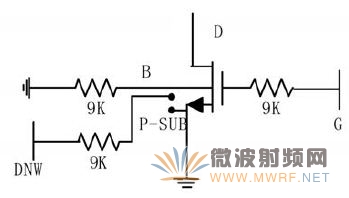

圖3 寬帶射頻收發開關設計原理圖

圖3所示為該寬帶射頻收發開關設計的電路原理圖,該電路在典型的串并聯結構基礎上,采用體懸浮技術的深N阱工藝的NMOS器件。從圖中可以看出,晶體管M2 和M4串聯,中間為天線端,M1和M3并聯在接收端RX和發射端TX。該電路收發兩路完全對稱,所有器件均采用深 N阱1.8V 薄氧型RFNMOS管。

在整個電路中,晶體管M2和M4起開關作用,用于選擇電路的收發狀態。當VDD為1.8V,VSS為-1.8V時,晶體管M2、M3導通,M1、M4截止, 開關處于接收模式,此時RF信號從天線流入到RX端。由于源漏電容Cds的存在,部分信號會從M4耦合到電路Tx端。此時M3處于導通狀態,可以將M4耦 合過來的信號導通到地,由此便提高了開關的隔離度。當VDD為-1.8V,VSS為1.8V時,開關處于發射模式,與接收模式的原理基本相同。電阻R1、 R5、R7和R12與NMOS管深N阱相連接,用于給深N阱加偏壓;柵極電阻R3、R6、R9和R11用來提高隔離度;R2、R4、R8和R10接晶體管 體端,用于體端懸浮。并且,為了進一步提高隔離度,所有體懸浮電阻的阻值都應足夠大。

本寬帶射頻收發開關電路中,晶體管M1、M3尺寸為96μm/0.18μm,M2、M4尺寸為200μm/0.18μm,電阻R1~R12均為9K ohm。該電路采用Cadence SpectreRF 對開關電路進行電路設計、仿真優化。

2、測試結果

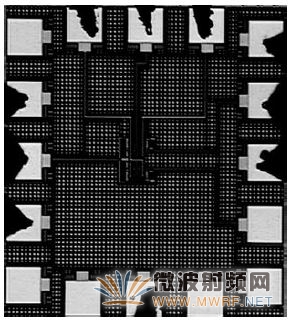

本開關電路設計采用GLOBALFOUNDRIES 0.18μm CMOS工藝。開關電路核心面積為0.015mm2,包括芯片測試焊盤的整體面積為0.53mm2,圖4為該射頻收發開關芯片顯微照片。本次芯片片上測試 環境基于Cascade Summit 探針平臺,如圖5所示,采用Rohde & Schwarz的矢量網絡分析儀ZVA40,使用TOSM(through-open-short-match)方法進行儀器校準。測試過程中,深N阱偏 置電壓VCC始終為1.8V, 控制電壓VDD和VSS為1.8V或-1.8V。輸入、輸出采用GSG射頻探針進行片上測試。

圖4 射頻收發開關芯片照片(接收狀態)

圖5 射頻收發開關測試平臺照片

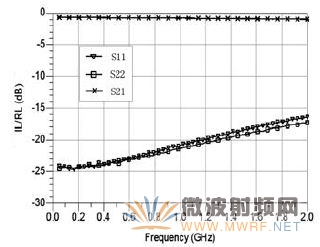

圖6 接收模式下插入/回波損耗測試結果

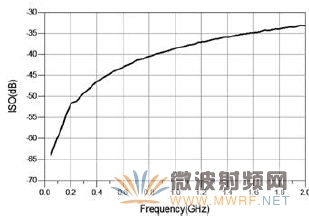

圖7 接收模式下隔離度測試結果

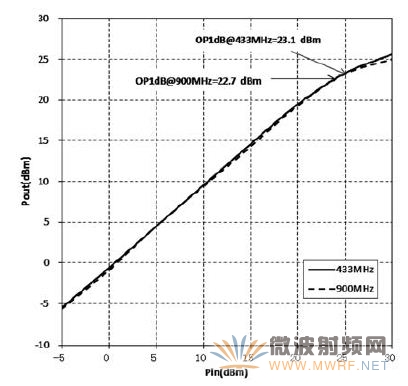

圖6和圖7均為該射頻開關在接收狀態下S參數測試結果。從圖6中可以看出,在0.1-1.2GHz頻段范圍內,開關的插入損耗(S21)為-0.7dB左 右,且平坦度良好,輸入、輸出回波損耗(S11和S22)小于-20dB;從圖7中可以看出,在整個頻段內射頻開關的隔離度(S13)均大于37dB,具 有良好的隔離特性。由于采用全對稱結構,該射頻開關在發射狀態下的S參數測試結果與接收狀態下相比基本相同。圖8所示的為該收發開關在433MHz及 900MHz頻率下的輸出功率曲線及1dB壓縮點。測試結果表明,兩個頻率的輸出功率曲線1dB壓縮點分別為23.1dBm和22.7dBm,且功率壓縮 特性基本一致。

圖8 輸出1dB壓縮點測試結果

結束語

本文設計了一種性能良好的超寬帶全集成CMOS 射頻收發開關芯片,芯片總面積為0.53mm2。測試結果表明,在1.8V電壓供電條件下,該射頻開關在0.1-1.2GHz頻段內收發兩路均可達到 0.7dB左右的插入損耗,小于-20dB的回波損耗以及優于37dB的隔離度。并且,在433MHz和900MHz頻率下可分別實現23.1dBm和 22.7dBm的線性度。該電路滿足0.1-1.2GHz頻段無線寬帶射頻收發芯片的基本設計需求,并適用于RFID和GSM-R系統中的典型應用。

粵公網安備 44030902003195號

粵公網安備 44030902003195號