利用7GHZ頻率合成器實(shí)現(xiàn)快速鎖定、高靈敏度的IF調(diào)諧無(wú)線接收機(jī)

前言

為了提高現(xiàn)代無(wú)線設(shè)備的靈敏度和可選擇性,需要盡可能地減小相位噪聲和參考雜散,并縮短鎖定時(shí)間。本文中所述電路可以改善本振(LO)的所有這些性能。

相位噪聲是對(duì)LO信號(hào)的純度的一種量度。相位噪聲是載波功率相對(duì)于給定的頻率偏移處(頻率合成器通常定義1kHz 頻率偏移)1-Hz的帶寬上的功率。其計(jì)算結(jié)果以dBc/Hz為單位表示。

由于頻率合成器內(nèi)部的開(kāi)關(guān)切換,輸出信號(hào)中會(huì)出現(xiàn)雜散(spurs)。在整數(shù)N分頻的合成器中,它們一般是由于鑒相器(PFD)的工作頻率點(diǎn)上的信號(hào)分量所引起的;在小數(shù)N分頻中,它們是由合成器本身架構(gòu)的特點(diǎn)所造成的。在整數(shù)N分頻鎖相環(huán)(PLL)中,它們被稱為參考雜散(reference spurs)。

鎖定時(shí)間是指輸出從一個(gè)頻率切換到另一個(gè)頻率所需要花費(fèi)的時(shí)間——這對(duì)于許多系統(tǒng)來(lái)說(shuō)是一個(gè)重要的指標(biāo)。一般說(shuō)來(lái),當(dāng)輸出穩(wěn)定到所期望的最終頻率附近、差異在某一百分比[或者以百萬(wàn)分之一(ppm)衡量]之內(nèi),或是相位鎖定在所需要相位度數(shù)的附近,此時(shí)我們說(shuō),輸出被切換到或者鎖定到新的頻率上了。

傳統(tǒng)的接收機(jī)實(shí)現(xiàn)方式

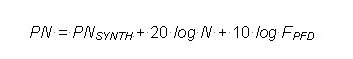

圖1所示的是最通用的的接收機(jī)架構(gòu)的功能框圖(超外差接收機(jī))。這里所示出的系統(tǒng)是滿足DCS1800移動(dòng)電話標(biāo)準(zhǔn)接收機(jī)的典型結(jié)構(gòu)。在該標(biāo)準(zhǔn)中,接收(Rx)頻段是1805MHz~1880MHz。

圖1中,RF輸入信號(hào)先流經(jīng)一個(gè)RF濾波器,接下來(lái)再經(jīng)過(guò)一個(gè)低噪聲放大器(LNA)。隨后,信號(hào)在混頻器中與一個(gè)可調(diào)諧的LO輸入進(jìn)行混頻,變換到中頻段(IF)。混頻后的信號(hào)接受進(jìn)一步的濾波,在通過(guò)一個(gè)最終的混頻器,與一個(gè)固定頻率的LO信號(hào)混頻,從固定的IF頻段下變頻到基帶信號(hào)頻段上。

可調(diào)諧的RF LO信號(hào)是利用一路干凈和穩(wěn)定的參考頻率信號(hào)來(lái)生成的,該基準(zhǔn)信號(hào)輸入至ADF4106 PLL合成器和一個(gè)壓控振蕩器(VCO)中后最終形成LO信號(hào)。參考頻率信號(hào)可以由溫補(bǔ)晶振(TCXO)、壓控晶體振蕩器(VCXO)或者恒溫晶體振蕩器(OCXO)來(lái)產(chǎn)生。 在整數(shù)N分頻系統(tǒng)中,PLL合成器的R分頻器將該參考信號(hào)變換成為一個(gè)頻率等于信道間隔的信號(hào)——或者,在小數(shù)N分頻系統(tǒng)中,將信號(hào)頻率變換成信道間隔的倍數(shù)。PFD則對(duì)環(huán)路輸出FVCO除以N后的結(jié)果與R分頻器的輸出進(jìn)行比較,然后,環(huán)路驅(qū)動(dòng)VCO,使得FVCO = FPFD × N,以使PFD輸出歸零。可以通過(guò)改變N來(lái)改變LO輸出頻率,從而對(duì)無(wú)線電路進(jìn)行調(diào)諧。

LO的相位噪聲取決于多方面的因素:參考信號(hào)噪聲、合成器中的噪聲(R分頻、N分頻、PFD和電荷泵),N值,以及PFD的工作頻率。

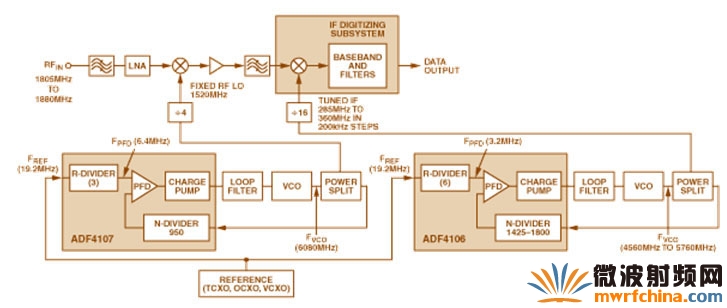

LO的相位噪聲(dB)可以用如下的公式來(lái)表示:

式中

PNSYNTH是合成器對(duì)相位噪聲的貢獻(xiàn)(在數(shù)據(jù)手冊(cè)中給出,單位是dB)

20 logN是合成器中的N值所帶來(lái)的附加噪聲

10 logFPFD是合成器的PFD頻率所產(chǎn)生的噪聲分量

*欲獲得更多詳情,請(qǐng)參閱“Design a Direct 6-GHz Local Oscillator with a New, Wideband, Integer-N, PLL Synthesizer”(Analog Dialogue, Volume 35, No. 6, November-December, 2001)

參考雜散取決于如下因素:PFD設(shè)計(jì),PFD電路中電荷泵的漏電,PLL環(huán)路帶寬,VCO靈敏度。鎖定時(shí)間取決于PFD頻率和PLL環(huán)路帶寬。

在接收機(jī)中, 如果IF選定為230MHz,經(jīng)過(guò)調(diào)諧的RF信號(hào)將在2035~2110MHz范圍內(nèi)變化(使用高端注入),步進(jìn)為200kHz。如果使用整數(shù)N分頻架構(gòu)來(lái)實(shí)現(xiàn)的話,則需要使用200kHz的PFD頻率,而N值將從10175(2035MHz)變化為10550(2110MHz)。

在商業(yè)應(yīng)用系統(tǒng)中所期望的帶內(nèi)相位噪聲為-85.6 dBc/Hz,采用適合的鎖相環(huán),如ADF4106,系統(tǒng)的典型基準(zhǔn)寄生為-88dBc @ 200kHz和-90dBc @ 400kHz。

圖1 傳統(tǒng)的超外差接收機(jī)的系統(tǒng)框圖

如果環(huán)路帶寬選取為20kHz,則相位差小于10度時(shí)對(duì)應(yīng)典型的鎖定時(shí)間將為250µs。

接收機(jī)的另一種可替代方案

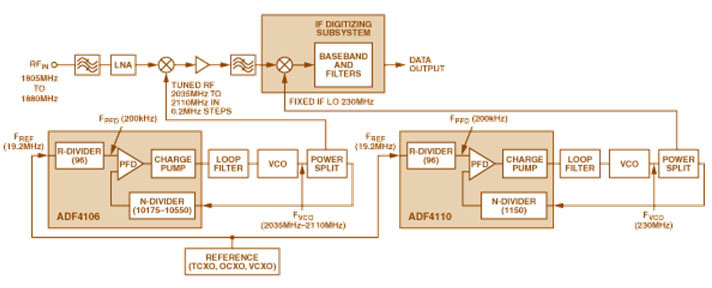

ADI公司目前提供一種新的寬帶寬PLL合成器——ADF4107。其RF級(jí)可以在高達(dá)7.0GHz的頻率下工作,而PFD頻率可以高達(dá)104MHz。這樣的寬帶寬工作能力可以用于實(shí)現(xiàn)新穎的接收機(jī)架構(gòu),如圖2所示。在該結(jié)構(gòu)中,每一級(jí)的LO都可以從一路頻率為所需頻率的整數(shù)倍的信號(hào)變換得到。此外,調(diào)諧是在IF部分完成的。這就容許系統(tǒng)采用非常高的倍率,以便改善總的相噪聲和鎖定時(shí)間性能。

固定頻率的RF電路

在圖2中,一個(gè)頻率固定的RF LO將信號(hào)向下變頻到IF頻段,而信道的調(diào)諧在IF中完成。仍以DCS1800為例,我們可以選擇頻率固定為1520MHz的RF LO。這可以從一路6080MHz的信號(hào)通過(guò)÷4分頻來(lái)獲得。

圖2 替代性的接收機(jī)框圖

RF LO 的相噪聲為:

–219 + 20 log 950 + 10 log (6.4 × 106) – 20 log 4

= –219 + 59.5 + 68 – 12

= –103.5 dBc/Hz

參考雜散將出現(xiàn)在偏離載波6.4MHz的頻率上,量值很小(<-90dBc),這是因?yàn)椋╝)4分頻電路對(duì)應(yīng)12dB的衰減,以及(b)——由于這是固定頻率的LO——環(huán)路帶寬可以變得很小(例如20kHz)。簡(jiǎn)單地施加一路20dB/十倍頻程的衰減,將可以進(jìn)一步衰減寄生分量。

在200kHz、400kHz、600kHz和800kHz處將不存在參考雜散,而鎖定時(shí)間也不成問(wèn)題,因?yàn)樵陬l率固定的RF電路中無(wú)需進(jìn)行任何調(diào)諧操作。

調(diào)諧作用的IF電路

我們繼續(xù)討論DCS1800實(shí)例,圖2示出了一種可調(diào)諧的IF電路,其調(diào)節(jié)范圍從285MHz到380MHz,步進(jìn)為200kHz。為了實(shí)現(xiàn)此功能,PFD頻率選用為3.2MHz ,相應(yīng)產(chǎn)生的初始LO信號(hào)可以從4560變化到5760MHz,調(diào)諧的步進(jìn)為3.2MHz。對(duì)這些頻率進(jìn)行16分頻,就可以獲得所需要的285MHz~360MHz、步進(jìn)為200kHz的信號(hào)。

可調(diào)諧的IF電路在最差情形下的位相噪聲為:

–219 + 20 log 1800 + 10 log (3.2 × 106) – 20 log 16

= –219 + 65 + 65 – 24

= –113 dBc/Hz

參考雜散將出現(xiàn)在偏離載波3.2MHz處。通過(guò)選擇500kHz的環(huán)路帶寬, 在3.2MHz的雜散將低于-90dBc。在一個(gè)DSC系統(tǒng)中,參考雜散件小的的重要頻率點(diǎn)是200kHz、400kHz、600kHz和800kHz。不過(guò)在我們所提出的配置中,這些頻率點(diǎn)上并不存在寄生分量,因?yàn)槲覀冞x用的PFD工作頻率高達(dá)3.2MHz。

在環(huán)路帶寬設(shè)定為500kHz, PFD頻率為3.2MHz時(shí),系統(tǒng)可以在10 µs以內(nèi)完成鎖相操作,且偏差在10°以內(nèi)。圖3所示的是頻率鎖定的響應(yīng)特性。

圖3 可調(diào)諧的IF電路鎖定時(shí)間

濾波方面的考慮

上述的兩種架構(gòu)實(shí)質(zhì)上都屬于超外差,采用了兩級(jí)下變頻電路。在每一級(jí)電路中,濾波都有著關(guān)鍵性影響。

在圖1中,位于LNA之前的RF濾波器可以抑制很強(qiáng)的帶外干擾,IF濾波器可以選用窄帶(在GSM體制中可以為200kHz)來(lái)抑制帶內(nèi)干擾。

在圖2中,RF濾波器與圖1中所示的相同。不過(guò),圖2中的IF濾波器不能采用窄帶的。它必須能覆蓋整個(gè)信號(hào)帶寬,因?yàn)檎{(diào)諧是在其后才發(fā)生的。這意味著,帶內(nèi)干擾信號(hào)將在信號(hào)鏈后面的基帶處理中濾除。ADI可以提供若干種IF到基帶的接收機(jī),包括AD6650、AD6652、AD9870和AD9874。在使用如圖2所示的架構(gòu)時(shí),應(yīng)該仔細(xì)考慮這些器件的選用。

結(jié)論

讓PLL的內(nèi)核以更高的PFD頻率工作(最終的LO頻率的整數(shù)倍)可以改善相位噪聲、輸出參考雜散和鎖定時(shí)間性能。另外,可調(diào)諧的IF架構(gòu)可以提供更高的性能,因?yàn)槠浔额l可以采用更高的整數(shù)倍。不過(guò),需要精心考慮濾波方面的需求。

本文中所示的例子是針對(duì)整數(shù)N分頻鎖相環(huán)ADF4107的,但這種結(jié)構(gòu)并不僅限于此,采用小數(shù)N分頻體系結(jié)構(gòu),也能實(shí)現(xiàn)類似的性能改善。

作者:Mike Curtin,Paul O'Brien,ADI半導(dǎo)體

參考文獻(xiàn)

Mini-Circuits Corporation, VCO Designer’s Handbook 1996.

Couch, L. W., Digital and Analog Communications Systems. New York: Macmillan Publishing Company, 1990.

Vizmuller, P., RF Design Guide, Artech House, 1995.

Best, R. L., Phase-Locked Loops: Design, Simulation and Applications, 3rd edition, McGraw Hill, 1997.

Bannerjee, Dean, “PLL Performance, Simulation and Design,” National Semiconductor Website.

Analog Devices, Inc. Data Sheet for ADF4107.

Hittite Microwave Corporation. Data Sheet for HMC362S8G

Curtin, Mike, “Phase-Locked Loops,” 3-part series in Analog Dialogue 33-3, 33-5, and 33-7 (1999). Also in hard copy: Analog Dialogue Volume 33, 1999.

Goldberg, Bar-Giora, Digital Frequency Synthesis Demystified, LLH, 1999.

粵公網(wǎng)安備 44030902003195號(hào)

粵公網(wǎng)安備 44030902003195號(hào)