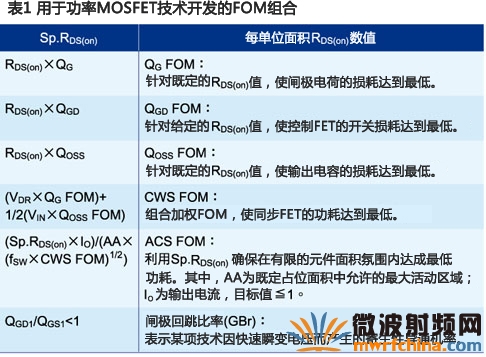

分析顯示,在研發功率MOSFET技術的過程中,以往常見以QG和QGD(即RDS(on)×QG和RDS(on)×QGD)為基礎的因子(FOM)已無法滿足需求,若堅持采用固定因子,將可能導致技術選擇無法達成優化。通過此次分析的啟示,工程師們已定義一套FOM以應用于新的低壓功率MOSFET技術研發。由此產生的30伏特(V)技術以超級接面(Superjunction)為基礎概念,是DC-DC轉換器的理想選擇;相較于橫向和分裂閘極溝槽MOSFET等競爭技術,該技術可同時提供特定的低RDS(on)、QG、QGD、QOSS和高度閘極回跳抑制。

MOSFET損耗問題加劇 催生新功耗分析技術

多相同步降壓轉換器是微控制器(MCU)以及其他運算密集型集成電路(IC),如數字信號處理器(DSP)和繪圖處理器(GPU)供電的拓撲結構選擇。在同步降壓轉換器內,兩個功率MOSFET串聯形成半橋結構。高處的MOSFET做為控制單結型FET;低處的MOSFET則為同步FET。

此電路拓撲演變的關鍵點在于2000年時,引進Pentium 4微處理器以及相關的ATX12V電源規范,其中的功率軌(即轉換電壓)從5伏特提高至12伏特,以達成微處理器需要快速增加電流的要求。因此而產生的工作周期變化使得功率MOSFET在性能優化方面發生重大變革,并全面采用QGD×RDS(on)和QG×RDS(on)等效益指數作為功率MOSFET的性能指針。然而,過去10年以來,特定尺寸產品中此類FOM和RDS(on)已降低約十倍,QG和QGD已不再是影響功率MOSFET功耗的主要因素。

就控制FET而言,MOSFET封裝和印刷電路板(PCB)聯機的寄生電感所產生的功耗可能超過由QGD產生的損耗。降低寄生電感的需求推動Power SO8封裝的普及化,并使整合動力的概念于2002年產生,即將控制和同步FET與MOSFET驅動器整合于四方形平面無接腳封裝(QFN)中,此概念于2004年獲英特爾(Intel)DrMOS規范采用。

為解決功率MOSFET多面性的損耗問題,一系列日趨復雜的運算方式和效益指數逐被提出。在功耗機制研究領域中,最被看好的技術是利用如TSuprem4和Medici等TCAD工具制作詳細的行為模型,并結合詳細的電路仿真(如PSpice),進而產生詳細的功耗分析結果。雖然此方法可針對不同的功耗機制進行深入分析,但分析結果需轉換成一套以MOSFET參數為基礎的FOM,以用于新技術的研發。

確認效益因子有助技術優化

前三項性能指針已廣泛用于評估技術的適用性,因此無需多作介紹,其僅用于告知設計工程師需盡可能減少單位面積上的RDS(on)值(即Sp.RDS(on)),以確保芯片在有限的封裝尺寸內達成最高的功效。且對于特定的RDS(on),要盡量降低MOSFET電容CGS和CGD,以達成最低開關損耗。

設計一款高性能MOSFET需在特定的參數之間做出權衡。例如,欲改善RDS(on)×QGD,可通過加大單元間距、犧牲Sp.RDS(on)而完成,還可通過增加一個連接源極的閘極屏蔽、犧牲RDS(on)×QOSS而完成。為避免產生不符理想的組件結構,需綜合這些FOM。此概念已被應用于生產綜合加權同步FET(FET CWS)FOM,即綜合考慮閘極電荷和輸出電容功耗的效應。此種FOM組合有助于對組件性能做出更精確的評估,此外,通過將轉換電壓和閘極驅動電壓(VIN和VDR)合并后,QG和QOSS的相對重要性取決于應用方式,進而確保改善后的閘極電荷不會對輸出電容產生不利影響,反之亦然。

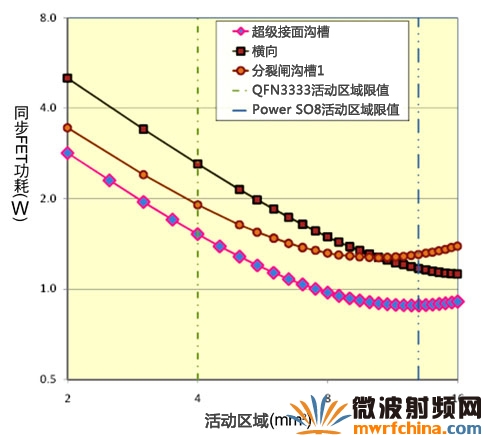

隨著小尺寸封裝芯片(如QFN3333)和多芯片產品(如DrMOS)的使用越來越為廣泛,將低Sp.RDS(on)與低開關FOM相結合的確有其必要性。面積限制同步(Area Constrained sync, ACS)FET FOM組合即是通過降低RDS(on)以提高開關性能,因此需要比封裝允許值更大的活動區域。請注意,該FOM不僅是一項單純的性能指針,而且關系到該技術是否有能力達成各項性能指針在特定空間限制下所認定的潛能。因此,在進行技術比較時,需留意此點。

在理想狀態下,對于CWS和ACS FOM而言,QG應在VDS=0和VGS=4.5伏特的條件下進行測量。若無法達成上述條件,可根據閘極電荷曲線,利用公式1計算QG。公式中的QG1、QG2分別為VDS1和VDS2條件下測得的閘極電荷,此兩點均取自于閘極電荷曲線中QGD的部分之后。

QG=4.5V×(QG1-QG2)/(VDS1-VDS2)‥‥‥‥(公式1)

QOSS=5.45×COSS(Vm)×(Vm+0.7)1/2‥‥(公式2)

最終的目標是確保MOSFET不會因為電容性電流流過閘漏電容(CGD)而導致寄生性導通,當快速VDS瞬變電流產生時,CGD會向CGS電容器充電,致使其電壓超過閾值。閘極回跳比率(Gate-bounce Ratio, GBr)即用于此目標;其本質在于,當漏極電壓升至輸入電壓電平時,如果所有流經CGD電容器的電容性電流都流入MOSFET的CGS,這時,CGS電容器的電壓仍必須低于電壓閾值。此一比例可利用QGD1和QGS1的值從閘極電荷曲線中輕易取得,其中,QGD1是VDS=VIN(CGD徹底充電)和VDS=VGS(CGD已放電)之間的QGD部分,QGS1為VGS=0至電壓閾值之間的QGS部分。

對于控制FET方面而言,由于現代功率MOSFET的高增益特性,其電流升降時間由電路和源極電感決定,因此其余能耗則由電壓升降時間決定,而這些時間則取決于QGD FOM。因此,單獨為控制FET定義一個FOM組合并無實際益處。雖然CWS FOM可達成優化以應用于同步FET,也可用于判定COSS、CGD和CGS之間由于裝置結構所產生的不利影響,但是要注意的是,由于現代組件的QGD相當低,因此,QGD不再是控制FET中功耗的主要因素。另外,由于控制FET的體積相對較小,基本上面積限制芯片尺寸的問題已不復存在,因此,采用面積受到限制的FOM亦無法增加優勢。

功率MOSFET結構各有優劣

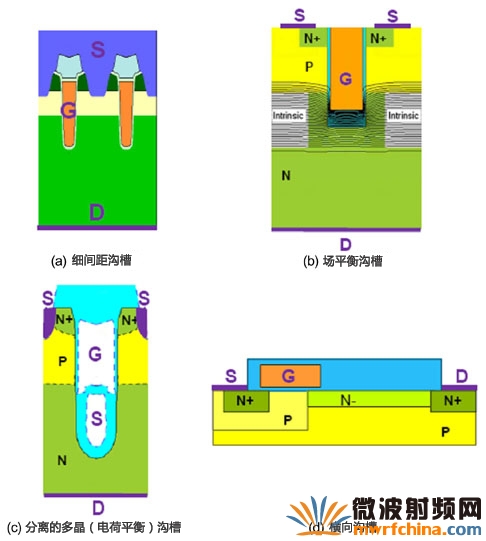

圖1標示出目前常用的多種功率MOSFET組件結構。圖1a中所示的高密度溝槽結構采用較低的Sp.RDS(on),但QG和QGD較高,因為此兩個參數與單元密度成正比。此種結構通常用于開關損耗較無重要性的應用中(如電池保護)。可通過加大單元間距、于溝槽底部加上厚氧化膜以改善此結構的開關性能。

因單元間距加大而導致的Sp.RDS(on)上升的問題,可針對MOSFET漂移區進行設計處理以解決,如圖1b所示的場平衡結構。目前最常采用的結構為分裂閘極(或電荷平衡)溝槽MOSFET,如圖1c所示。此種結構閘極的正下方采用一個連接源極的屏蔽電極,既可降低QGD,且通過應用降低表面電場(RESURF)原理,漂移區的電阻降至最低。當然,此結構也有其缺點,其需要較高的單元密度(因此閘極電容較高)以獲得RESURF狀態;另外,采用連接源極的屏蔽電極將產生額外的QG和QOSS,并增加制程的復雜程度。

相反地,和溝槽結構相比,橫向MOSFET結構(圖1d)由于可采用RESURF技術且毋需增加單元密度,因此,可達成出色的QG和QGD FOM。但由于橫向結構需要將漂移區納入單元間距中,因此,可達成的單元密度較低,導致Sp.RDS(on)較低,進而影響到在小面積封裝中為同步FET提供所需低RDS(on)的能力。

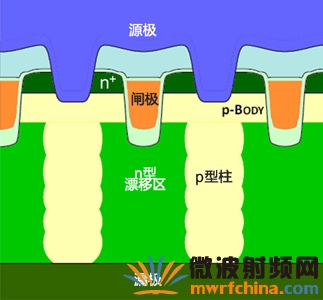

圖2 低壓超級接面結構

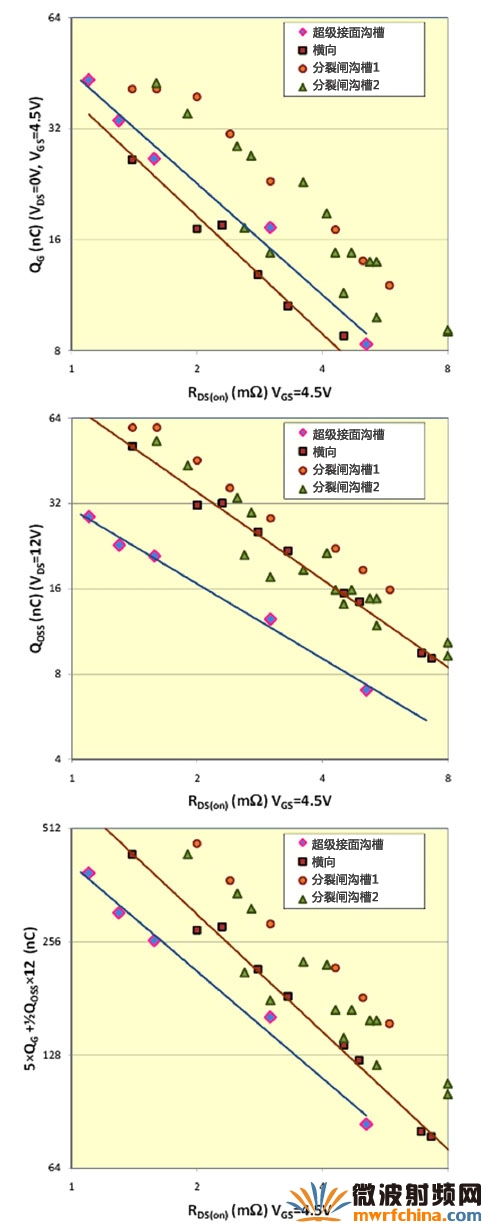

橫向/分裂閘/超級接面FOM比較

相較于采用表面漏極觸點的橫向組件而言,橫向結構的基板與漏極連接,并在組件主體和基板間增加CDS組件,可產生較高的QOSS結構。分裂閘結構的QOSS值亦較高,因為其依賴漏源極電容的產生以屏蔽閘極電極,達到低QGD和RDS(on)。而超級接面結構毋需增加額外的CDS組件,因此可達成三種結構中最低的QOSS值。

對于同步FET方面,也必須要針對Sp.RDS(on)進行權衡和取舍,因為即便在高開關頻率下,導通狀態下的損耗仍占大部分比例。圖4顯示不同技術下RDS(on)與芯片面積的關系。顯而易見,橫向結構需要更大的芯片才得以獲得與溝槽結構相同的RDS(on)。若觀察競爭對手產品的最低典型RDS(on)值(VGS=4.5伏特時),將會發現,橫向技術可達成的最佳結果為1.4毫歐姆(mΩ)(CSD17312Q5)、分裂閘結構可達成1.1毫歐姆(FDMS7650),而超級接面結構可達成1.1毫歐姆(PSMN1R0-30YLC)。就Sp.RDS(on)而言,競爭產品的基準顯示,當VGS=4.5伏特時,橫向技術單位面積的RDS(on)值較超級接面技術和分裂閘技術的RDS(on)值高出60%。如圖3所示,由于芯片的尺寸不一,上述差異并未充分反映出實際上最低的RDS(on)值。請注意,CSD17312Q5的額定閘極電壓為10伏特,而溝槽技術為20伏特。如果采用相同的額定閘極電壓組件進行RDS(on)比較,則其差異將更明顯。

封裝面積縮小帶來更多挑戰

PL=IO2RDS(on)×tf×dt+fSW (VDR×QG0+1/2VIN×QOSS)‥‥‥‥‥(公式3)

PL=IO2/AA×Sp.RDS(on)+AA×fSW (CWS FOM)/Sp.RDS(on)‥‥‥‥‥‥‥(公式4)

Sp.RDS(on)×IO=AA×(fSW(CWS FOM))1/2‥(公式6)

(Sp.RDS(on)×IO)/(AA×(fSW×CWS FOM)1/2)=1‥(公式7)

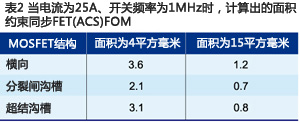

表2列出針對Power SO8和QFN3333封裝的ACS FOM。對于Power SO8來說,分裂閘技術的ACS FOM最低,代表其最佳性能最易于達成。但由于CWS FOM值為最大(圖3),因此,并非最佳的技術選擇。值得注意的是,雖然分裂閘結構的開關FOM不如橫向技術,但由于橫向技術的Sp.RDS(on)較差,因此無法充分利用其開關FOM方面的優勢。相反,在這三項技術中,超級接面結構同時擁有最低的Sp.Rds(on)和CWS FOM,因而能夠在所需芯片面積內發揮最佳性能。當采用更小的QFN3333封裝時,這些技術均無法發揮其最佳性能(三者的ACS FOM>1)。然而,圖4所示的結構中,明確標示出需要進一步降低Sp.RDS(on),盡管這樣做可能導致開關FOM變差,詳見分裂閘技術和橫向技術針對面積小于4平方毫米應用的對比。

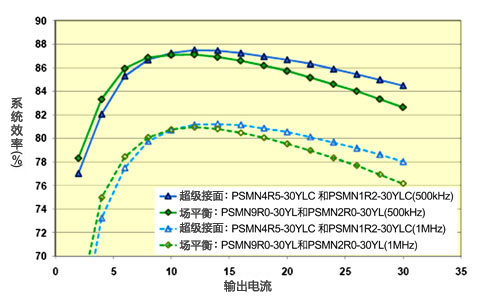

為展現超級接面功率MOSFET結構的優點,可對系統效率進行測量,并將測量結果與超級接面組件和芯片尺寸相似的場平衡結構組件做比較,工作頻率為500kHz和1MHz、電壓從12伏特轉換為1.2伏特(圖6)。當二者的芯片尺寸相同時,前者的導通狀態損耗優于后者。當工作頻率為500kHz和1MHz時,在30安培全負載和低負載條件下,系統效率均提高2%。超級接面芯片尺寸無論大小,均有可能出現下列情形,如重負載條件下的效率提升會犧牲輕負載效率,而輕負載條件的系統效率提升會犧牲重負載效率。采用RDS(on)較高的控制FET可能會改善效率,因為QGD降低所帶來的益處大于RDS(on)升高所帶來的壞處。

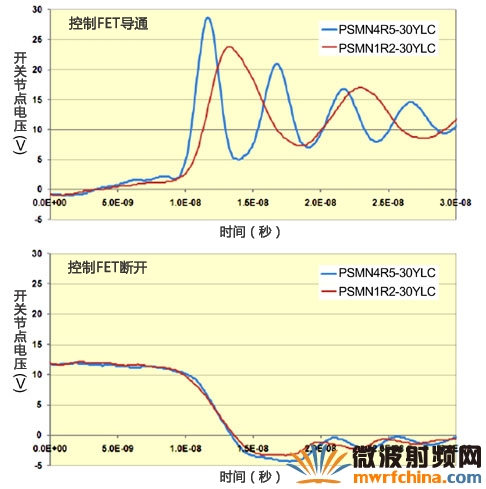

從上述中可知,控制FET的開關速度可能會受到QGD以外的其他因素限制。可從圖7明顯看出,低RDS(on)同步FET(PSMN1R2-30YLC)與中等RDS(on)同步FET(PSMN4R5-30YLC)的開關波形的比較。在這兩個例子中,PSMN4R5-30YLC均作為控制FET。可明顯地看出,開關節點(即控制FET和同步FET形成的半橋中點)的上升時間與控制FET無關。換言之,開關節點電壓上升所導致的導通損耗不再受控制FET的QGD限制。

本例中的限制因素為電路通過寄生電感為同步FET的輸出電容充電所需要的時間。結果顯示使用者必須更加重視降低QOSS,而非CWS FOM隱含的值。斷開操作是控制FET功耗最集中的時候,此時低RDS(on)和中等RDS(on) MOSFET的開關節點電壓壓降幾乎是沒有差別,這表示開關時間仍然受高側組件的QGD影響。由于閘極電流比較低,且MOSFET閘極電阻具有內部分配性,控制FET的斷開速度通常較慢于導通速度。因此控制FET極可能是決定組件斷開時開關速度的影響因素。

新的FOM被用于分析三種不同的功率MOSFET結構。結果顯示最近開發的低壓超級接面結構可完美結合低RDS(on)、低QG和低QGD等特性,其性能優于橫向和分裂閘等競爭產品結構。此外,隨著封裝尺寸縮小,ACS FOM亦顯示出在功率MOSFET設計中,犧牲Sp.RDS(on)以改善開關頻率并非為最佳策略。

粵公網安備 44030902003195號

粵公網安備 44030902003195號