當恩智浦半導體(NXP Semiconductors N.V.,NXP)開始使用先進的低功率芯片設計技術時,有一件事令其大吃一驚。“某些情況下,在實現階段出現了兩倍的產能下降。”NXP公司設計與技術負責人Herve Menager表示。

從整個行業來看,這并不是一個特例。雖然EDA供應商們一直在為兩種競爭性的低功率規范爭斗不休,但它們似乎忽略了一個更大的問題:類似多電壓設計等低功率技術如此困難,以至于設計人員需要重新考慮整個芯片的設計流程。在最近于加州Monterey舉行的電子設計過程(EDP)大會上,Menager和其它芯片設計師詳細探討了這方面的挑戰。

EDA供應商們理解設計師所處的兩難境地。“產能帶來的影響是巨大的。”Cadence設計系統公司Encounter營銷副總裁Eric Filseth說,“低功率技術不能單靠版圖,這是架構方面的事,涉及驗證、實現、測試等整個設計階段。”

大多數觀察人士認為,業界已經確立了諸如門控時鐘和多電壓閥值(multi-Vt)等一些基本的低功率設計技術,而且它們也得到了現有工具的支持。門控時鐘通過限制時鐘分配來減少動態功率,多電壓閥值設計在非關鍵性能處使用高電壓閥值單元來降低漏電流。

設計師遇到的難題在于怎樣利用更先進的多電壓技術。在采用多電壓供電(multi-Vdd)方法時,一些模塊的供電電壓要低于其它模塊,從而形成電壓“孤島”。這種情況在靜態電壓時已經非常復雜,而當采用動態電壓調整方法在工作期間改變電壓值時,會變的更加復雜。

為了降低漏電流,一些設計采用功率選通法并通過多閥值CMOS(MTCMOS)開關關閉不在使用狀態的模塊。在這里,上電和斷電順序的設計和驗證可能會特別復雜。

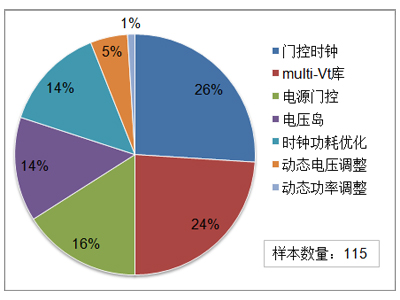

先進的技術也在不斷迎頭趕上。在2006年設計自動化會議上,由Sequence Design公司撰寫的調查報告指出,有26%的受訪者表示正在使用門控時鐘,另有24%使用的是multi-Vt庫(參見圖1)。

圖1、設計人員正在使用電壓島、電源門控和其他功率控制技巧

“多電壓和電源關斷等先進技術會影響到整個設計流程。”新思公司RTL綜合和低功率產品部營銷總監Gal Hasson表示。

設計挑戰

Menager在EDP會議上指出,截至目前,NXP已經嘗試借助兩種方法來解決動態功率問題,分別是通過門控時鐘降低功耗,以及減小開關電容。最近,該公司開始使用電壓島和頻率調整方法來滿足性能和功率要求。

多電壓設計通常需要:電平轉換器,讓信號跨越電源域邊界;保持寄存器,在斷電時保持狀態信息;片上開關,實現加電和斷電;隔離單元,在斷電時控制輸出。這些技術NXP都在使用,但針對電路單元的自動實現和驗證的詳細意圖卻非常復雜,Menager表示。

例如,電平轉換器引入的版圖約束會極大提高CAD工具的復雜性,Menager表示。雖然版圖在邏輯上是正確的,但在物理方面卻可能出錯,他指出。

Menager表示,當隔離鉗位二極管用于電源開關時,可能傳輸不必要的數據,而浮置輸入端也可能發生短路。保持寄存器可能需要緩存樹對控制信號“常開”,而電源連接不僅容易出錯,而且非常耗時,他說。

Menager認為,電壓島可以利用片上開關打開或關閉,但這樣做會使電源分配和底層規劃變得更為復雜。開關需要合適的尺寸來平衡電流承載能力與面積和漏電流二者之間的關系,有必要使用靜態IR壓降分析來驗證這個尺寸。

在SoC級,全局緩沖策略和電源分布是很復雜的,Menager指出。

低功率設計對可測試設計(DFT)影響很大,Menager指出。在電壓島間插入掃描鏈會大量增加復雜性。

“我們需要對后端實現具有更少破壞性的靈活解決方案。”Menager說,“重要之處在于捕獲,且在早期正確捕獲電源網絡的意圖。”

通用功率格式(CPF)對捕獲電源意圖至關緊要。據Menager透露,NXP已經使用了Si2的CPF,并發現其極具價值。但在CPF和Accellera的統一功率格式(UPF)之間的標準之爭卻是個令人頭疼的問題。

“好消息是我們終于從無格式發展到有格式,”Menager說,“壞消息卻是,我們一下子從一無所有跳躍到有太多選擇。”

當時鐘變得復雜

飛思卡爾半導體公司也使用多電壓技術,其GSM手機的待機電流和工作電流正在以每年大約15%的速度下降,設計經理Milind Padhye表示。Padhye指出,采用多電壓設計法后,設計中的未用部分其電源可以被切斷;低性能部分可以工作在較低電壓下。不過,這樣做也存在著成本問題。

“對多電壓設計而言時鐘是一個最大的挑戰。”Padhye表示,“電壓促使時鐘移位。當時鐘開始移位時,時序就會出現混亂。最終可能需要上百個邊界條件來優化時序。”

Padhye認為,為了達到高效的電壓分割,需要采用架構分析方法,并且系統必須經過多次驗證,包括斷電過程中、斷電完成后以及上電期間。“假設你創建的某個事務在斷電狀態下終止,而且現在芯片也不工作了,”Padhye說,“你如何進行調試?這就好似對一個死者詢問‘你能告訴我你是如何死亡的嗎’一樣。”Padhye宣稱,避免1個電源缺陷相當于避免10個功能性缺陷。

針對保持驗證,設計人員必須確認狀態被正確保存和被正確恢復,而且系統能在上電后正常工作。針對電壓和頻率變化,設計人員必須驗證系統性能狀態、電壓變化,以及變化期間和變化后的系統操作。

Padhye指出,整個流程能始終支持低功率技術是很重要的。雖然飛思卡爾公司正在使用CPF,但最終還是希望業界能夠采用統一的功率格式,Padhye表示。

更高抽象層

TI公司科學家Mahesh Mehendale也贊成在低功率設計中采用系統級方法。他的EDP演講綜述了多標準、多格式視頻處理器SoC面臨的低功率設計挑戰。

據Mehendale透露,TI公司在SoC級的電源管理策略包括:自適應電壓調整,可根據工藝和溫度最小化電壓;動態電源切換,可在不同電源模式間切換以減少漏電流;動態電壓和頻率縮放,可調整電壓和頻率來適應性能要求;多電壓域;以及靜態漏電管理。

Mehendale指出,技巧在于找到頻率與公共集電極電壓間的“功率最優化”工作點。較低的Vcc有助于動態和泄漏功率,但如果Vcc下降但是頻率保持不變,那么門數量將會上升,從而有悖于任何功率節省方案。如果在架構級進行選擇,優化的MHz/Vcc折衷可驅動對并行和管線機制的需求。

“功耗問題需要在所有抽象級加以解決。”Mehendale說,“其在系統和架構層的影響尤其顯著。”

包括Cadence、新思和Magma在內主要的IC實現工具供應商都表示,他們正在改善對先進的低功率設計技術的支持。今年早些時候,Cadence在CPF基礎上推出了一款低功率設計流程。由Cadence公司開發的這一流程正在推進標準化,它在綜合、驗證、形式等效性檢查、DFT和物理版圖方面都有效融合了功耗意識。

目前Cadence尚未提供的功能是系統級低功率設計。“這是一定要做的事,”Filseth說,“架構和系統級是獲得功率節省的主要場合。”

新思公司的所有綜合優化功能(包括DFT)都具有“功率意識”,Hasson表示。為了支持多電壓設計,新思的綜合工具可以確定保持、隔離和電平轉換單元。在物理實現方面,新思的電源網絡規劃工具可以執行電壓下降分析,它的版圖工具可以正確放置電源開關。

Magma設計自動化公司兩年前就提供了一體化的低功率設計流程,Magma公司低功率產品部產品經理Arvind Narayanan表示:“Herve Menager談到的multi-Vdd流程在系統中是自動實現的。”

供應商們表示,多年來對低功率設計的支持一直是EDA產業的優先考慮對象。“這并不是對現有工具的功能追加,” Filseth認為,“而是對設計流程該如何工作的重新通盤考慮。”

粵公網安備 44030902003195號

粵公網安備 44030902003195號