隨著雷達和無線通信系統中的信號處理從模擬轉向數字,已經為開發先進的波束形成技術實現新的應用付出了巨大的努力。快速傅立葉變換是最常見的一種使用數字方法精確引導波束能力的方法,這導致雷達和通信系統的設計方式發生了重大變化。

波束成形技術可分為自適應波束成形和切換波束成形技術。在切換波束成形中,例如,通信基站從預設的波束中選擇波束,每個波束基于接收信號的強度來指向特定方向。當用戶相對于天線陣列移動時,信號被切換到陣列中的其他陣元上,這些陣元可以更好地在特定方向上提供更強的信號。

自適應波束成形技術在另一方面依賴于實時計算,這是一種允許基站在目標用戶的方向上發送更聚焦的波束,同時減少其他方向上的輸出,從而大大減少陣元間干擾。

自適應波束成形設計需要更高的處理帶寬,每秒必須執行數十億次乘法和累加運算。因此,它在接收端抑制噪聲源和干擾方面變得非常重要。同時,必須保持天線陣列中每個陣元的實時方向控制。為了實現這一點,有必要使用陣元級處理來單獨地和同時地對每個天線陣元接收的信號進行數字處理。

由于需要大量的計算負荷,傳統的CPU和DSP在自適應波束成形應用中可能會迅速負擔過重。然而,由于其嵌入式DSP模塊,并行處理架構和增強的存儲器功能,具有更高性能的FPGA非常適合這項任務。

全球對移動寬帶數據和語音服務需求的不斷增長,促使無線網絡運營商需要不斷擴展和升級他們的網絡,以提供更多容量。運營商正努力將每個無線基站可支持的用戶數量最大化的同時,降低基礎設施成本,并為用戶保持極具吸引力的價格點。

由于可用無線頻譜的數量有限,這種努力變得復雜,因此增加的流量會產生更多的干擾,并且由于天線技術的限制,呼叫質量部分會受到影響。全向天線通常用于蜂窩塔上的發射和接收。然而,在這種傳統的方法中,天線充當換能器,將電磁能轉化為電能,效率低,并且受到高度干擾的影響,由于單個塔上存在多種信號,所以干擾會降低整體連通性。

通過使用在同一塔上組合在一起的定向扇形天線,可以減輕這種干擾。這些自適應陣列天線或智能天線已越來越多地用于電信網絡中,以改善無線連接質量并提高整體容量。

這是通過波束成形技術實現的,該技術通過使用先進的數字信號從各個用戶的基站引導波束處理。波束成形調整每個輸入和輸出信號的功率和相位,以產生沿特定方向傳播的波束,同時減少非必要輸出。這減少了各個信號相互之間的干擾,并提高了所有連接的質量。

創新的自適應波束形成算法的出現導致浮點運算在信號處理中的使用增加,從而通過實現目標的實時跟蹤來最小化干擾并提高雷達容量。這是通過使用諸如QR分(QRD)和權重反向替換(WBS)的算法同時同時創建多個點波束來實現的。

這些算法有助于自適應地形成波束,同時降低噪聲和干擾,但它們每秒需要進行大量的浮點操作。

由于許多雷達系統的尺寸,重量和功率受到限制,使用傳統的CPU或GPU并不是最佳方法,因為執行浮點計算所需的硬件數量增加。由于需要更多的存儲器,功率和空間,因此使用多個CPU對雷達系統的設計具有重大影響,更不用說更高的成本,更復雜的系統設計和更長的集成時間。基于CPU的進一步設計受到有限內存和接口選擇的限制。

FPGA采用先進的數字波束成形技術,可以降低成本,復雜性,功耗和上市時間,因此與采用先進數字波束成形技術的雷達系統中的CPU和GPU選項相比具有巨大的優勢。由于FPGA具有在自適應波束成形應用中處理高度并行浮點運算的卓越能力,因此FPGA可以提高算法性能,同時顯著降低功耗。

FPGA也是一種更有效的選擇,因為單個器件通過天線陣中每個陣元捕獲的信號在PCIe和串行RapidIO等I / O標準上接收和處理大量數據,除了提供更高性能的處理之外,這樣的系統還消除了對需要超過1000瓦功率的VPX機箱中容納的大量耗電,多核CPU板的需求。簡化的單FPGA設計還受益于外部存儲器和單板上的其他額外功能,功耗低于80瓦。

數十年來在軍事和國防應用中,常見的智能天線和自適應波束成形的使用在商業蜂窩網絡中并不廣泛,直到相對最近,由于與廣泛部署相關的過高成本。 隨著低成本FPGA和DSP的興起,自適應波束成形在2000年代早期進入3G移動基礎設施,該技術現已廣泛用于擴展4G網絡。

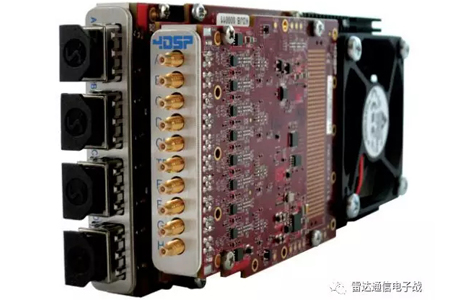

使用與FPGA板卡緊密耦合的高性能模擬收發器 (如4DSP基于Xilinx Virtex-7的FM788) 為硬件,frmware設計人員開辟了可以在商業和國防應用中使用波束成形方法的新的機會。

粵公網安備 44030902003195號

粵公網安備 44030902003195號