引言

單片化、模塊化、現代化是現代接收機技術的發展趨勢,包括通信領域、雷達領域及其他相關領域的接收機。但是,由于各種新型器件的研發周期越來越短,要求雷達接收機的更新換代也就越來越快,這就給接收機系統設計提出了新的、更高的要求。而在傳統接收機系統設計中,數字電路的設計、仿真已經非常成熟,其RTL、系統級的仿真工具已經大量出現;但在模擬電路設計方面,這種高層次仿真、綜合工具還相對落后,以前基本依靠系統工程師自身多年經驗甚至直覺來進行模擬前端設計,根本沒有優化與分配[1],嚴重約束了系統開發周期。

隨著電路結構的日趨復雜和工作頻率的提高,在電路與系統設計的流程中, EDA軟件已經成為不可缺少的重要工具。EDA軟件所提供的仿真分析方法的速度、準確與方便性便顯得十分重要,此外該軟件與其他EDA軟件以及測量儀器間的連接,也是現在的龐大設計流程所必須具備的功能之一。Agilent公司推出的ADS軟件以其強大的功能成為現今國內各大學和研究所使用最多的軟件之一。本文的系統設計方法正是基于ADS軟件進行仿真分析的。

系統設計方法

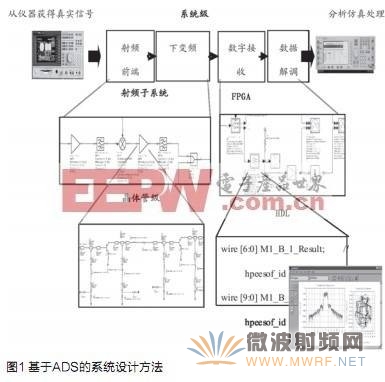

本文提出的系統設計方法從系統整體入手,將整體指標通過預算分析分配給不同的模塊,獲得各模塊具體指標后就可以進行各模塊的具體設計,然后驗證其可行性,進而大大縮短設計時間,提高設計的可靠性,避免了重復工作和資源浪費。此種方法消除了以往設計方法的盲目性,將采用定量優化的方法,自頂而下進行設計,如圖1所示。傳統設計一般是自下而上,先設計每個單元模塊,再把它們組合成系統整體。這樣做一方面有可能達不到總體要求;另外一方面,為了滿足整體指標,加大了單元模塊設計的難度;此外,對于不同的系統要求和標準,還必須重新設計,費力而且費時。采用自頂向下的設計方法則完全避免了這些問題。

系統結構的優化選擇

如今的雷達接收機系統在符合各種不同標準的同時必須在各種信號鏈路中滿足嚴格的指標要求。根據雷達接收機預先設定的性能指標進行系統結構的優化選擇,首先對各種接收機結構性能進行仿真分析,得到粗略的性能極限標界;同時,根據關鍵性能指標建立系統優化理想行為模型,并利用大量已測產品行為模型進行修正。比如,要對系統進行鏈路預算仿真,預估整體性能是否滿足接收機系統要求,同時作為器件選取依據。

雷達接收機的常規結構如圖2所示。

在傳統接收機結構設計基礎上可以從頻譜利用率高低方面[2][3]對接收機結構進行分類,在此只簡單介紹中等頻譜利用率的接收機結構。

此種結構中,未使用頻帶數和系統占用的大致相等,因此射頻前端應該支持在數個頻帶上的同時并行感知活動。從電路觀點來看,接收機組成器件數目大大增加。從實際應用考慮,并行處理路數應控制在4或5路為佳。此時,需要大功率精確控制多路本振信號,而它們又需要在固定頻率上工作,因此要求也相應的很寬泛。為了做到并行一致性,可用頻率必須足夠多,同時在ADC之后可以采用通道校準算法進行通道校準[4]。因此,并行通道的基帶端口增大了帶寬,這就比低頻譜利用中需要更高速率和分辨率的A/D轉換器。

綜上所述,不同的系統結構,其性能指標極限和集成度是不同的,而指標極限和集成度又隨著工藝的改進而變化。因此,進行系統結構優化選擇時,還必須考慮未來工藝、電源電壓以及電路結構的演變對優化模型的影響。

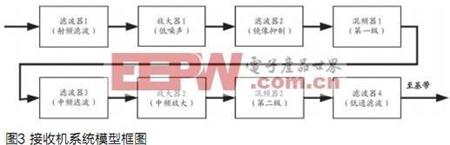

中等頻譜利用率接收機結構的系統模型如圖3所示。

從而得到系統結構性能向量為:

其中A1表示中等頻譜利用率接收機結構性能向量,f1、f2、f3、f4分別代表各濾波器的性能函數,a1、a2代表各放大器的性能函數,m1、m2代表各混頻器的性能函數。

通過類似的方法,可以分別得到低頻譜利用率和高頻譜利用率接收機結構的性能向量A2、A3,并最終通過優化函數:

得到最優接收機系統結構。

通過這個仿真,將看到系統總增益在系統各個部分的分配情況。預算增益仿真在諧波平衡分析以及交流分析中都可以進行,但如果在交流仿真中進行的話,混頻器不能是晶體管級的。這里進行的是行為級仿真,混頻器的非線性特征是已知的,因此需要用交流分析來進行仿真[4][5]。

仿真會在接收機總增益最大和最小兩種情況下進行以便得到較為全面的分析結果。當VGA增益為最大值時,信號源的功率電平為接收機的靈敏度-113dBm(已考慮了天線雙工器的損耗);反之,當VGA的增益最小時,信號源應輸入接收機所能接收的最大功率。這些參數的變化都要在VAR中設置出來。

可以在原框圖的基礎上設置預算路徑并建立預算方程,筆者兩次仿真的結果,如圖4(a)和4(b)所示,可以清楚地看到接收機在VGA增益最大和最小的情況下整機增益的分配情況。

由圖4還可以看出,接收機前端一般要有AGC的加入,以便動態調節輸入信號的輸入功率,使之匹配ADC。

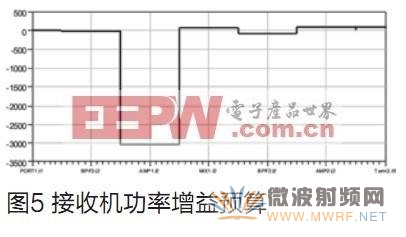

圖5所示為接收機功率增益預算,從圖中可以看出功率增益在各個器件上的分配情況。

射頻模塊的優化選擇

在系統結構的優化選擇中,已經得到最優的系統結構。而系統性能指標無法直接應用于結構規劃和模塊設計,需要把這些指標轉換為能直接反映射頻模塊性能的參數,如噪聲系數、線性度、穩定性等,因此可以分配具體的性能參數到各射頻模塊中去。

射頻模塊一般都可以分為放大、濾波、混頻等模塊,以放大器為例,其實際的行為模型還必須考慮各種非線性因素。

噪聲。可以認為是與有用信號不相關的隨機干擾,主要有熱噪聲、散粒噪聲和閃爍噪聲三種類型。接收機的噪聲系數主要取決于它的前端電路,若無高頻放大器,主要由混頻電路決定。

線性度。用來衡量線性度的指標主要有三階交調、二階交調和1dB壓縮點。

穩定性。因晶體管都存在著內部反饋,當反饋量達到一定程度時,將會引起放大器穩定性變壞而導致自激。

這些非線性因素不是孤立的,而是與輸入信號疊加在一起共同組成系統的輸入輸出。用Sideal、Sn、Sl、Ss分別表示模塊的理想信號、噪聲、線性度、穩定性,則其輸入、輸出信號可以分別表示為

從而可以得到實際器件的行為模型,并結合ADS仿真分析其性能。

器件選型

在此只對一些典型器件如射頻濾波器、低噪聲放大器等進行仿真、分析。

濾波器

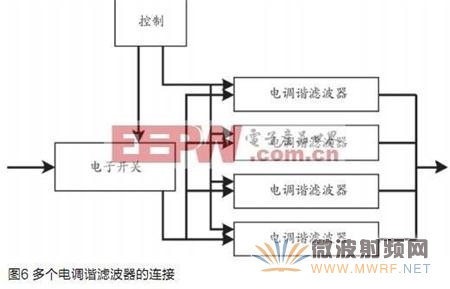

由于是對天線接收下來的微弱射頻信號直接濾波,因此要求射頻濾波器的插損和帶內波動等都盡可能小。為了滿足系統性能要求和提高接收機設備的動態范圍,通常需要幾組濾波器,以減少干擾信號的數量和幅度,以及進入接收機的噪聲。同時為了覆蓋整個頻段,采用電調諧濾波器是必然趨勢。電調諧濾波器是通過改變濾波網絡中的可變電容,來實現網絡頻率響應的變化。利用電壓改變可變電容的容量,達到所需要的頻率響應。本設計中,每個頻段可以分別用一個電調諧濾波器來覆蓋。

多個電調諧濾波器的連接如圖6所示,其輸入信號為天線接收下來的射頻信號,輸出信號為經過電調諧濾波器選擇的信號,可以滿足對濾波器(包括射頻濾波器和中頻濾波器)的超寬帶要求。因此,利用電子開關和信號處理器的控制端口,就可以把濾波器置于帶內任意感興趣的頻段。

低噪聲放大器

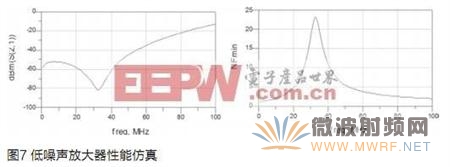

根據所要求的靈敏度、帶通濾波器插損和ADC輸入電平的要求,設計放大器的增益和匹配等問題。在搭建電路時尤其要注意電源旁路、寄生電容和外圍器件的選擇對充分發揮低噪聲放大器性能的影響。本文可以利用ADS軟件,按照參數要求,自行設計一個低噪聲放大器,并對其參數進行優化、仿真,得到如圖7所示的仿真結果。從結果可以看出,此低噪聲放大器基本滿足設計要求,可用于系統設計中。接著可以根據軟件設計的結果繪制電路版圖,并加工成電路板。最后對加工好的電路進行調試,使其滿足設計要求,此項工作將在以后完成。

把上述設計方法與傳統的基帶等效系統優化方法結合起來,就形成了一個自上而下、能全面評價系統結構性能的設計流程。

結語

本文在常規接收機設計方法的基礎上,利用ADS軟件,提出了一種高效的系統設計方法。經過驗證,大大縮短了雷達接收機系統的開發周期,并且目前已逐步在筆者所在課題組項目中應用。

參考文獻:

[1] 支傳德,楊華中,汪蕙. 射頻前端接收機頻率規劃[J]. 電路與系統學報, 2006(8):21-25

[2] Ramanathan R, Patridge C. Next Generation(XG) Architecture and Protocol Development(XAP).AFRL-IF-RS-TR-2005-281 Final Technical Report.2005(8)

[3] 楊小牛, 樓才義, 徐建良. 軟件無線電原理與應用[M]. 北京: 電子工業出版社, 2001

[4] 龔廣偉. 無線接收機前端設計及多通道校準技術研究[D]. 國防科技大學碩士學位論文, 2008

[5] 高峻. 無線通信射頻接收前端研究與設計[D]. 西南交通大學工學碩士學位論文, 2006

粵公網安備 44030902003195號

粵公網安備 44030902003195號