在一個高速印刷電路板(PCB) 中,通孔在降低信號完整性性能方面一直飽受詬病。然而,過孔的使用是不可避免的。在標準的電路板上,元器件被放置在頂層,而差分對的走線在內層。內層的電磁輻射和對與對之間的串擾較低。必須使用過孔將電路板平面上的組件與內層相連。

幸運的是,可設計出一種透明的過孔來最大限度地減少對性能的影響。在這篇博客中,我將討論以下內容:

· 過孔的基本元件· 過孔的電氣屬性

· 一個構建透明過孔的方法

· 差分過孔結構的測試結果

1. 過孔結構的基礎知識

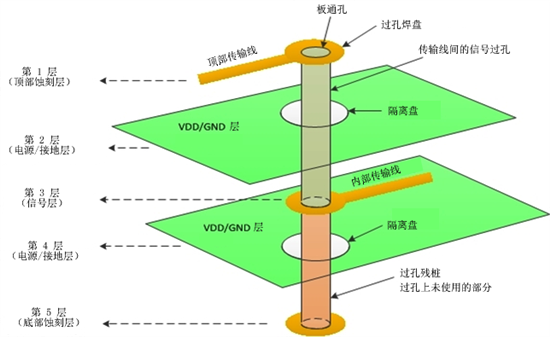

讓我們從檢查簡單過孔中將頂部傳輸線與內層相連的元件開始。圖1是顯示過孔結構的3D圖。有四個基本元件:信號過孔、過孔殘樁、過孔焊盤和隔離盤。

過孔是鍍在電路板頂層與底層之間的通孔外的金屬圓柱體。信號過孔連接不同層上的傳輸線。過孔殘樁是過孔上未使用的部分。過孔焊盤是圓環狀墊片,它們將過孔連接至頂部或內部傳輸線。隔離盤是每個電源或接地層內的環形空隙,以防止到電源和接地層的短路。

圖1:單個過孔的3D圖

2. 過孔元件的電氣屬性

如表格1所示,我們來仔細看一看每個過孔元件的電氣屬性。

| 層 | 過孔元件 | 電氣屬性 |

| 層1(頂層) | 過孔焊盤 | 過孔焊盤在焊盤和下方的接地層之間引入寄生電容。 |

| 1-2層(過孔) | 信號過孔 | 過孔是一個電感器。 |

| 層2(平面層) | 隔離盤 | 隔離盤在金屬圓柱表面和附近的過孔周圍接地層之間產生邊緣電容。 |

| 2-3層(過孔) | 信號過孔 | 電感。 |

| 層3(信號) | 過孔焊盤 | 焊盤與其上下的接地層之間的寄生電容。 |

| 3-4層(過孔) | 過孔殘樁 | 過孔的未使用部分形成電容短截線效應。 |

| 層4(平面層) | 隔離盤 | 電容。 |

| 4-5層(過孔) | 過孔殘樁 | 過孔的未使用部分形成電容短截線效應。 |

| 層5(底層) | 過孔焊盤 | 電容。 |

表1:圖1中顯示的過孔元件的電氣屬性

一個簡單過孔是一系列的π型網絡,它由兩個相鄰層內構成的電容-電感-電容(C-L-C) 元件組成。表格2顯示的是過孔尺寸的影響。

| 相關尺寸 | 電氣屬性 | 對電容阻抗 (Zo) 的影響 | |

| 過孔焊盤 | 小焊盤直徑 | C↓ | Zo↑ |

| 過孔大小 | 小孔直徑 | L↑ | Zo↑ |

| 隔離盤 | 大隔離盤直徑 | C↓ | Zo↑ |

| 過孔長度 | 更長的過孔長度 | L↑ | Zo↑ |

| 電源/接地層 | 更多平面層 | C↑ | Zo↓ |

| 過孔殘樁 | 更長的過孔殘樁 | C↑ | Zo↓ |

| 過孔間距 | 更小的過孔間距 | C↑ | Zo↓ |

表2:過孔尺寸的直觀影響

通過平衡電感與寄生電容的大小,可以設計出與傳輸線具有相同特性阻抗的過孔,從而變得不會對電路板運行產生特別的影響。還沒有簡單的公式可以在過孔尺寸與C和L元件之間進行轉換。3D電磁(EM) 場解算程序可以根據PCB布局布線中使用的尺寸來預測結構阻抗。通過重復調整結構尺寸和運行3D仿真,可優化過孔尺寸,來實現所需阻抗和帶寬要求。

3. 設計一個透明的差分過孔

我們曾在之前的帖子中討論過,在實現差分對時,線路A與線路B之間必須高度對稱。這些對在同一層內走線,如果需要一個過孔,必須在兩條線路的臨近位置上打孔。由于差分對的兩個過孔距離很近,兩個過孔共用的一個橢圓形隔離盤能夠減少寄生電容,而不是使用兩個單獨的隔離盤。接地過孔也被放置在每個過孔的旁邊,這樣的話,它們就能夠為A和B過孔提供接地返回路徑。

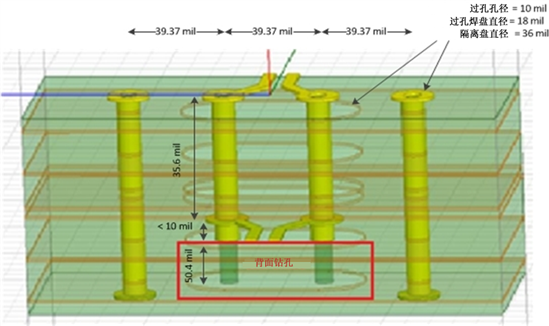

圖2顯示的是一個地-信號-信號-地(GSSG) 差分過孔結構示例。兩個相鄰過孔間的距離被稱為過孔間距。過孔間距越小,互耦合電容越多。

圖2:使用背面鉆孔的GSSG差分過孔

不要忘記,在傳輸速率超過10Gbps時,過孔殘樁會嚴重影響高速信號完整性。幸運的是,有一種背面鉆孔PCB制造工藝,此工藝可以在未使用的過孔圓柱上鉆孔。根據制造工藝公差的不同,背面鉆孔去除了未使用的過孔金屬,并最大限度地將過孔殘樁減少到10mil以下。

3D EM仿真器用來根據所需的阻抗和帶寬來設計差分過孔。這是一個反復的過程。此過程重復地調整過孔尺寸,并運行EM仿真,直到實現所需的阻抗和帶寬。

4. 如何驗證性能

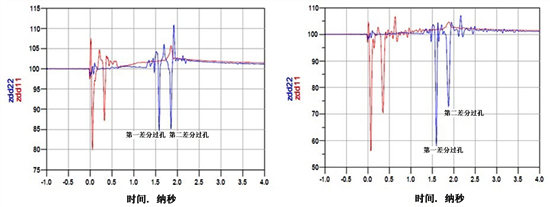

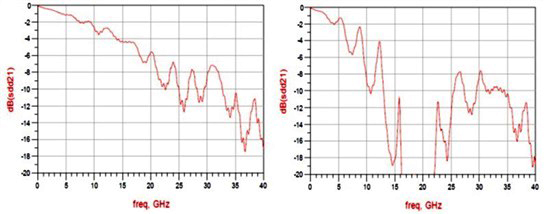

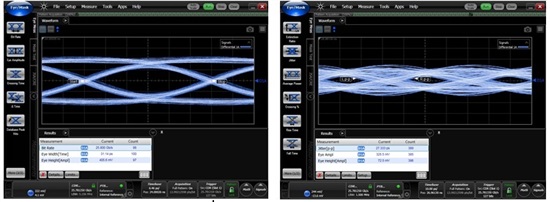

圖2中顯示的差分過孔設計已構建完畢并經測試。測試樣片包括頂層的一對差分線,之后是到內部差分線的差分過孔,然后第二對差分過孔再次連接至頂層的球狀引腳柵格陣列封裝(BGA) 接地焊盤。信號路徑的總長度大約為1330mil。我用差分時域反射儀(TDR) 測得其差分阻抗,用網絡分析儀測得了帶寬,并用高速示波器測量了數據眼圖來了解其對信號的影響。圖3,4,5分別顯示了阻抗、帶寬和眼圖。左圖是使用背面鉆孔時的測試結果,而右圖是無背面鉆孔的測試結果。在圖5中的帶寬波特圖中,我們可以很清楚地看到背面鉆孔對于在數據速率大于10Gbps 的情況下實現高性能是必不可少的。

使用背面鉆孔,ZDIFF大約為85? 無背面鉆孔,ZDIFF大約為58?

圖3:TDR阻抗波特圖

12.5GHz時的插入損耗大約為3dB 12.5GHz時的插入損耗大于8dB

圖4:頻率響應

使用背面鉆孔時,數據眼是打開的 無背面鉆孔時,數據眼是關閉的

圖5:25Gbps時的數據眼圖

TI擁有豐富的高速信號調理集成電路 (IC)產品庫,諸如retimer和redriver。它們有助于減輕和緩解所有類型差分對的缺陷和高插入損耗,從而實現先進系統中的可靠數據通信并擴展傳輸距離。

來源:德州儀器

粵公網安備 44030902003195號

粵公網安備 44030902003195號