如何降低芯片功耗目前已經成為半導體產業的熱點問題。過去,對于集成器件制造商(IDM)來說,最直接的作法就是通過先進的制程工藝和材料比如低K介質來解決,低功率設計可以通過將自己設計團隊的技能和經驗進行結合而實現。

然而,當進入90nm后,漏電流問題日益凸現,CMOS靜態功耗驟增,功率管理開始成為一個重要的考慮因素。這種情況在65nm與45nm以下將更為嚴重,因為工藝節點的不斷縮減導致柵極氧化層厚度越來越薄,柵極泄漏呈指數增長,最終動態功耗等于亞閾值泄漏電流,也等于柵極泄漏電流。這就迫使業界必須從IC的設計端就開始采用低功耗設計技術。

為了應對這些挑戰,設計工程師們開始提倡采用復雜的時鐘門電路開關方案,從而減少了不必要的門電路開關操作。如今,為了滿足功率方面的目標,設計人員運用了各種先進的低功率設計技巧,包括多閾值設計、多電壓設計、動態頻率電壓縮放(DVFS)、時鐘門控、可感知功耗的內存以及功率門控等等。

在設計早期進行有效的功率評估

毋庸置疑,在產品成功因素中,面市時間是重要因素之一,有時甚至決定著產品的成敗。因此在設計早期解決潛在低功耗問題對于提高生產率是至關重要的。

Synopsys公司資深顧問工程師李昂表示,在設計早期(即系統架構階段)評估系統層面低功耗的策略和代價對于后面的實現非常重要。在這階段評估的低功耗策略主要應注意的方面包括:系統軟硬件的劃分、是否采用多電壓(multi-voltage)、是否采用電源關斷(multi-supply)、采用片上還是片外電源管理、低功耗IP的選擇等。在這階段的評估,一方面是通過對過往系統的評估經驗,一方面可以通過快速原型設計,通過Eclypse系統對設計原型進行功耗估算,以評價設計的代價和功耗節省的效果。

Cadence公司高級技術主管Brad Miller也表達了相同的觀點。他表示,以下五個方面將確保設計者高效而精確的達到他們的目標:1、確定設計中耗費功率的元器件;2、采用精確的開關行為數據;3、生成開關行為時考慮仿真模式;4、采用精確的線路模型;5、采用表示最壞情況功率的庫。

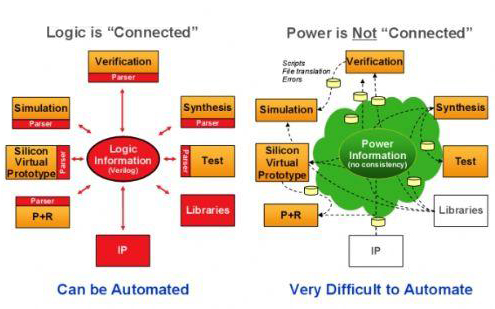

圖1:很多設計相對邏輯是“相連的”,但對功耗是“不相連”的,且不能自動完成設計

多種低功耗設計解決方案應對功耗挑戰

但是,不同低功耗技術的EDA支持是支離破碎的,結果設計師不得不通過一系列特殊手段定義低功耗功能。更重要的是,設計的可預測性和驗證變得極其困難。同時,由于設計上的復雜度以及以前缺乏EDA自動化手段的原因,工程設計團隊面臨著手工分析和運用這些技巧的難題,而且也沒把握在不影響性能的條件下滿足功耗預算目標。

Cadence公司相關人士就指出,目前的很多設計可以說對邏輯是“相連的”,因為所有流程都處理邏輯信息,可以自動完成;但對功耗來說是“不相連”的,因為針對每個流程,功耗問題都是獨立的,并相互影響。而且最重要的是還不能自動完成功耗設計,許多地方需要手動來完成。

因此,有效的低功率設計要求設計團隊、IP供應商以及工具和解決方案提供商之間展開協作。只有通過實施連貫一致的方法,并將這些方法運用在供應鏈賴以存在的整個工具領域,電子行業才能真正解決低功率設計所面臨的不斷增長的挑戰。

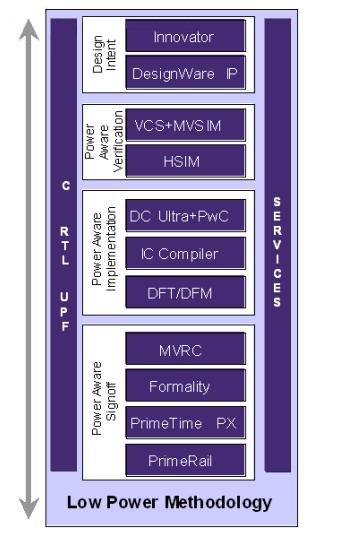

圖2:Synopsys Eclypse低功率解決方案

Synopsys Eclypse低功率解決方案

Eclypse解決方案支持標準的統一功耗格式(UPF)語言,并兼容低功率設計方法指南(LPMM)。采用了諸如MTCMOS功耗門控、多電壓、以及動態電壓和頻率縮放(DVFS)等多種低功耗設計技術,使工程師的芯片設計和驗證發生較大轉變。設計者可以利用增強的時鐘門控和低功耗時鐘樹綜合,在為低功耗而優化時鐘結構的同時,兼顧時鐘抖動和時序等目標;多閾值漏電流優化利用選項限制了Vt的比例,提供獨立于設計處理的最佳漏電流功耗優化;電源開關插入和優化的增強型自動化功能,使電壓降和面積限制能夠用于功耗規劃和假設分析。

Cadence低功耗設計方法學錦囊

Cadence公司的低功耗設計方法學錦囊(Cadence Low-Power Methodology Kit)提供了一個覆蓋邏輯設計、功能驗證和物理實現的端到端方法學,它使用Si2的通用功耗格式(CPF),在整個流程中提供單一的低功耗意圖規范。該錦囊包括了一個通用無線應用設計,實現時采用了多供電電壓和電源關斷技術等方法,并且包含了在整個端到端流程中承載設計意圖的相關指令腳本和技術文件。

這個錦囊是易于組合使用的,包括6個不同的流程:低功耗功能仿真、邏輯綜合、可測試性設計(DFT)和自動測試矢量生成(ATPG)、物理設計、形式實現、驗證和功耗網格簽收。用戶可以將該錦囊作為一個完整的流程來實施,或選擇單獨的選擇模塊使用。

圖3:Cadence低功耗設計方法學錦囊

IC設計低功耗標準之爭

從2007年伊始,圍繞針對低功耗IC設計的標準,兩大EDA陣營就展開了激烈競爭。一方是由Cadence公司開發、Si2(Silicon Integration Initiative)的低功耗聯盟(LPC)管理的CPF;而另一方是則是由Synopsys、Mentor Graphics和Magma Design Automation公司支持的UPF。UPF和CPF都允許用戶在整個RTL-to-GDSII設計流程中定義功率設計意圖和約束條件,并且二者的實現方法也非常相似。

Cadence 公司亞太區總裁居龍表示,CPF的優勢是就是以用戶為中心-用戶驅動、用戶采用。UPF標準是CPF的響應,最初因為一些專利問題,CPF沒有被置于公共領域(public domain)。但后來Cadence將其提交給了IEEE,使CPF能夠面向行業開放。他認為,從設計角度來看,完全沒有必要出現兩個標準,因為它們實際討論的是同一件事情。

Synopsys公司Bruce Jewett認為,UPF是一種開放式語言,其優勢是被IEEE看好。至于今后兩個標準是否會進行融合,兩家EDA巨頭均表示這完全取決于市場和商業利益,其實用戶真正關心的,是擁有確定的解決方案,能夠幫助他們解決目前遇到的問題。

而據日經BP社報道,瑞薩公司DFM及數字EDA技術部門總工程師井上善雄對兩個派系通過集中各種規格的EDA工具,從而構筑整個低功率設計流程的觀點提出了置疑。他表示:“如利用大量常見的普通工具構筑流程,會出現與CPF和UPF工具混在一起的情況。從這個意義上來說,CPF和UPF的整個流程都是紙上談兵。”

但另一個有趣的情況是,推出被井上稱作CPF和UPF的“超級組合”,同時支持靜態驗證和動態驗證規范的ArchPro公司在2007年6月被Synopsys收購。在此次Synopsys推出的Eclypse低功率解決方案中,我們就看到了MVRC、MVSIM等ArchPro工具的身影。可以預見,在未來一段時間內,雙方陣營勢必將圍繞低功率標準展開一番激烈的爭斗。

粵公網安備 44030902003195號

粵公網安備 44030902003195號