LVPECL(低壓正射極耦合邏輯)是一種輸入輸出(I/O)技術,從半導體工藝無法集成高性能P 型設備與高性能N 型設備起就已出現。因此,在隨后的HCSL 和LVDS等高速接口中,需要外部無源器件來完成由P 型設備完成的任務。

對LVPECL 而言,很少有人研究過完成輸出級設計所需要的發射極電流控制與傳輸線終端之間的關系。剖析LVPECL 閘道的基本原理和分析任何特定LVPECL 驅動器的典型終端,有助于工程師量身定制穩健和高能效的LVPECL 終端。

LVPECL 驅動器

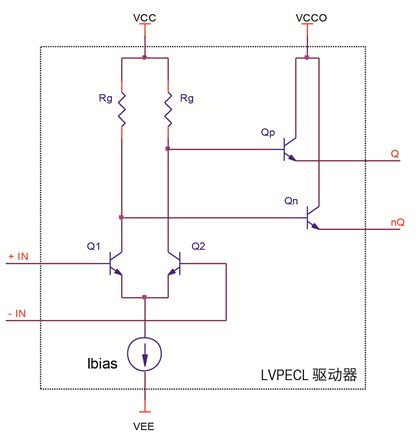

如圖1 所示,簡化的LVPECL 閘道通常用開放的發射極驅動器來實現。沒有Q 和nQ 晶體管的接地通路,這兩者隨后被關閉。

因此,輸出級必須由用戶通過外部元件來完成。

圖1、開放式發射極LVPECL驅動器等效電路圖

標準終端

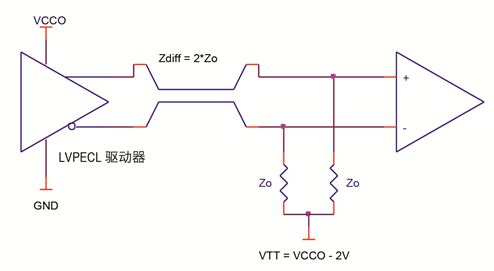

圖2 顯示標準的直流耦合LVPECL 終端。驅動器輸出電流由外部Zo 電阻器和VTT 終端電壓設定。由于VTT 終端電壓是由相對Vcco 的-2V 調節器產生的,輸出驅動器電流不受Vcco 變量的影響。主要缺點是需要調節器,盡管它確實可以將驅動器的發射極電流保持在第一階,不受Vcco 變化的影響。

圖2、標準的LVPECL終端

Thévenin 等效終端

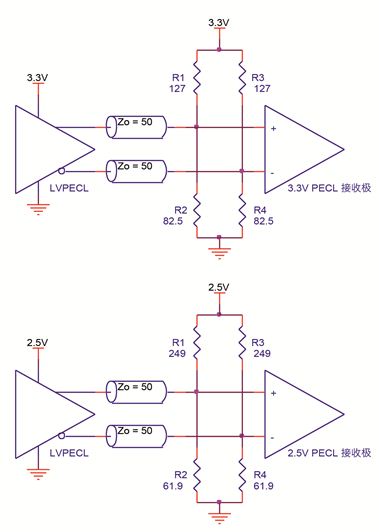

圖3所示用于提供3.3V 和2.5V 電流的備選Thévenin 等效終端,用兩個電阻串產生VTT 電壓,因而可以不再使用調節器,但也有缺點。

1)圖3 中的R1 和R2 偏壓電阻串需要大量功率損耗才能產生Thévenin 電壓。功率損耗取決于特定驅動器的高輸出電壓(Voh) 和低輸出電壓(Vol);參見以下“案例研究”章節。

2)Vcco 變化率通過偏壓分壓器前饋至Thévenin 等效VTT 電壓;39% 表示Vcco =3.3V,20% 表示Vcco =2.5V.因此,VTT 電壓只限在標稱Vcco 下才是正確的,發射極電流的控制不如標準VTT=VCC-2.0V 終端有效。

圖3、3.3V 和2.5V Thévenin 等效LVPECL終端

T 終端

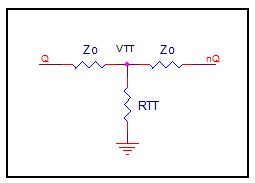

圖4 所示T 型電阻器網絡可以解決Thévenin 終端的許多不足。穿越RTT 的共模電壓被稱為VTT,相當于VTT = Vcco-2.0V.要記住,具體的VTT 電壓不屬于設計標準;LVPECL 接收極從不檢測VTT,但會檢測發射極電壓。VTT 只對標準終端具有重要意義,原因是VTT 向終端前饋VCCO 以控制發射極電流。相反,T 終端通過負反饋對發射極電流施加控制。圖4 LVPECL T 終端網絡中的VTT 電壓間接取決于特定LVPECL 驅動器的Voh 和Vol 電平,以及設計師為邏輯0 驅動器輸出選擇的最小發射極電流。

圖4、LVPECL T 終端網絡

1) T 終端由驅動器電源直接供電,因此消除了Thévenin偏壓串的功能損耗。

2) 通過共模阻抗向T 網絡VTT 電壓回饋的Vcco 變化率大于通過Thévenin 網絡回饋的變化率,因而可以更好地控制發射極電流。詳情請參見以下“發射極電流控制”章節。

3) 可以調節共模阻抗,并因此調節負反饋,以針對由于Vcco、溫度和設備處理等方面的變化而造成的Voh 和Vol 方面的變化穩定驅動器電流。

PI 終端

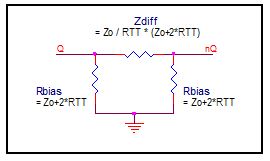

可以利用著名的電阻網絡星形三角關系,從T 終端產生等效的PI 終端。下圖5 顯示按T 網絡換算的PI 網絡的元素值。

圖5、PI 終端網絡

很少使用的PI 終端具有超越T 終端的布局優勢;它可以安全布置在頂層之上。T 的共模阻抗必須經由除頂層之外的其它層。

發射極電流控制

T 終端提供比Thévenin 終端更好的發射極電流控制。Thévenin 終端通過向終端產生的VTT 電壓前饋Vcco 變化率α來穩定電流。相反,T 終端通過檢測穿越發射極電阻器的發射極電流使用負反饋,只能用作單一的發射極跟隨器。

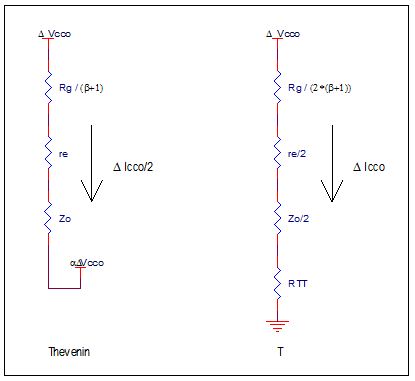

可按下圖6所示為每個終端構建每一個Vcco 變化的電路,來說明這種性能方面的變化。對于每一個終端,電路從Vcco 開始,穿過相應輸出晶體管的基極-發射極結Rg,然后穿過終端,Rg 在此被轉入發射極電流通路。為簡單起見,基極擴展電阻已被并入增益設置電阻Rg。由于有兩個偏壓串,Thévenin Icco 為總電流的一半。

圖6、Thévenin 和T 終端發射極電流控制電路

可從圖8 立即寫下每個電路的傳遞函數。在每個傳遞函數中,re 術語均已被棄用;與Rg 和Zo 相比,它相對較小。此外,re 規模小意味著T 終端的邏輯1 晶體管和邏輯0 晶體管的等效半電路是相同的。

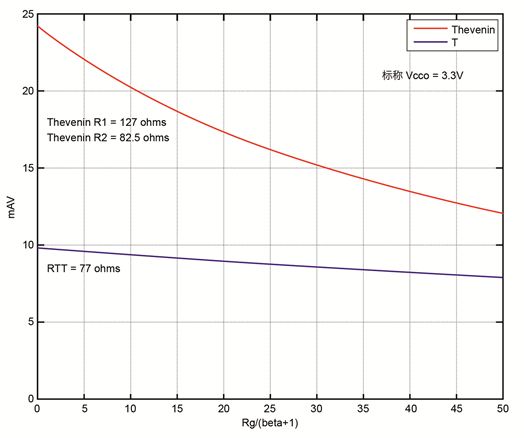

由于Rg 和 β的值取決于特定LVPECL 驅動器的內部設計和處理,以下列“案例研究”章節為預期,當VCCO = 3.3V 和RTT=77 ohms 時,這兩個傳遞函數是相對下圖8 中的Rg/(β+1) 而設計的。

圖7、發射極電流中適應Vcco 變化的Thévenin 和T 終端變化

比方說,如果Rg/(β+1) = 0,則 β值很大,而Rg 值小(圖1 中的Ibias 高)。在這種限定條件下,傳遞函數只取決于外部電阻器。更實際一點,如果Ibias = 0.5mA,Rg= 1.6 kohms,β=100,則Rg/(β+1) ≈16。

案例研究

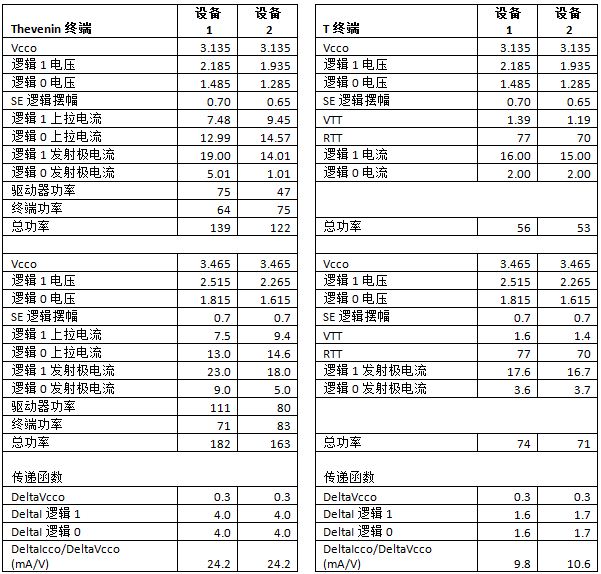

在 ±5% Vcco 的條件下,針對每一個終端比較了業界現有的具有不同Voh 和Vol 值的兩種不同的LVPECL 驅動器。T 終端將針對每一種設備經過優化,設計為當Vcco 為-5% 時,邏輯0 發射極電流至少達到2mA,以實現切換速度與功率之間的最佳平衡。對于每一個案例,電子表格的值用KVL 和KCL 進行計算。為進行全面核算,計算出每個案例中驅動器和終端的功率。

如下圖表1 所示,由于可以自由選擇T 終端的RTT,因而具有降低總驅動器電流的設計靈活性,同時還能保證最低的邏輯0 發射極電流。Thévenin 終端的固定電阻值則不然。請注意固定器件Thévenin 終端的Vcco 和設備上的邏輯0 發射極電流大波動。如果還考慮到設備處理和溫度所帶來的變化,兩種終端之間的差異將變得更加巨大。

所有電流和電壓均用3.3V 電源數據表中的典型Voh 和Vol 值進行計算。由于該數據表無其他說明,Voh 和Vol 隨Vcco 的變化假定為1:1。因此,這些案例等同于設置Rg/(β+1) =0。電流以mA 單位,功率以mW 單位。

表1、Thévenin 和T 終端兩種不同驅動器之比較

結論

在集成電路技術效力遠不如今的時代,LVPECL 作為一種高速輸入輸出標準面世。LVPECL 驅動器最后必需使用外部無源元件才能令人滿意,但它必須設計為與驅動器的輸出邏輯電平Voh 和Vol 相輔相成。眾所周知,已有的終端網絡有缺點。使用Pi 或T 電阻網絡可以克服這些缺點,實現適應性更強、更加節能的設計。

粵公網安備 44030902003195號

粵公網安備 44030902003195號