要滿足苛刻的頻率合成器要求,通常需要做到一定程度的設(shè)計靈活性。基本的鎖相環(huán)(PLL)頻率合成器能以低成本、高空間效率、低功耗封裝提供合理的頻譜純度和頻率捷變,因此它在射頻(RF)系統(tǒng)核心位置發(fā)揮作用已經(jīng)有段時間了。但是,在要求快速切換速度、低相位噪聲或低雜散信號電平的場合,有必要使用更為復(fù)雜的架構(gòu)。通過正確的設(shè)計方法,結(jié)合使用現(xiàn)代低成本高集成度的PLL和直接數(shù)字合成器(DDS)集成電路(IC)可以極大地促進高性能架構(gòu)的實現(xiàn)。

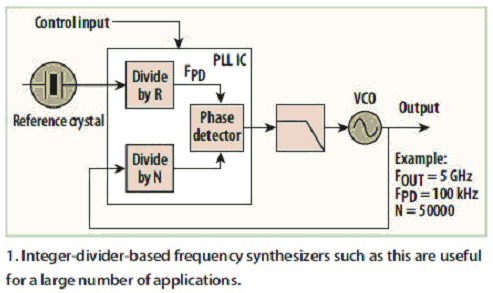

大部分高頻系統(tǒng)都使用傳統(tǒng)的基于整數(shù)分頻器的設(shè)計(圖1)或基于分?jǐn)?shù)N分頻器的設(shè)計。不管是使用哪種設(shè)計,聯(lián)合使用單個通用頻率合成器IC和一個外部壓控振蕩器(VCO)通常都可以實現(xiàn)要求的功能。VCO功能可以用IC、模塊或分立元件解決方案甚至在合成器芯片內(nèi)部實現(xiàn),具體取決于所要求的頻率范圍、相位噪聲性能以及空間、成本和功耗約束條件。最終設(shè)計通常以制造商的應(yīng)用筆記為基礎(chǔ),并且一般可以使用可下載的應(yīng)用程序完成合成器的寄存器加載和相位檢測器增益的設(shè)置等功能。

圖1、像這種基于整數(shù)分頻器的頻率合成器對許多應(yīng)用來說都非常有用。

不過,對于要求非常高的某些應(yīng)用來說,基本架構(gòu)的性能也許遠(yuǎn)遠(yuǎn)滿足不了要求,特別是在相位噪聲、雜散信號電平以及頻率切換速度方面。多普勒雷達(dá)系統(tǒng)中使用的頻率合成器以及工作在微波頻率、使用快速頻率切換和/或高階調(diào)制方案的通信系統(tǒng)就是這種應(yīng)用的很好例子。

舉例來說,如果一個應(yīng)用要求整數(shù)PLL合成器有高的輸出頻率、相對小的調(diào)諧步長(這意味著高的分頻比),這將導(dǎo)致環(huán)路帶寬內(nèi)產(chǎn)生很高的相位本底噪聲[因為相對于輸出的相位檢測器噪聲將增加20log(N)]。比如在5GHz輸出頻率和100kHz信道間隔情況下所需的分頻比是50000,這將導(dǎo)致94dB環(huán)路帶寬內(nèi)的本底噪聲超過相位檢測器的噪聲(在1Hz帶寬內(nèi)的典型值約為-75dBc)。典型的小數(shù)N頻率合成器IC在1Hz帶寬的噪聲指標(biāo)可以達(dá)到-85dBc左右。

雖然直接模擬頻率合成器(一般由開關(guān)可選的倍頻器、混頻器和濾波器組成)在切換速度和相位噪聲方面可能比較優(yōu)秀,但它們的實現(xiàn)通常太過復(fù)雜,特別是當(dāng)要求很好的雜散信號性能時。數(shù)字直接合成器(DDS)可以提供精細(xì)的調(diào)諧步長、快速頻率切換速度和良好的相位噪聲,但不采用額外倍頻器的話,無法直接提供微波頻率輸出。

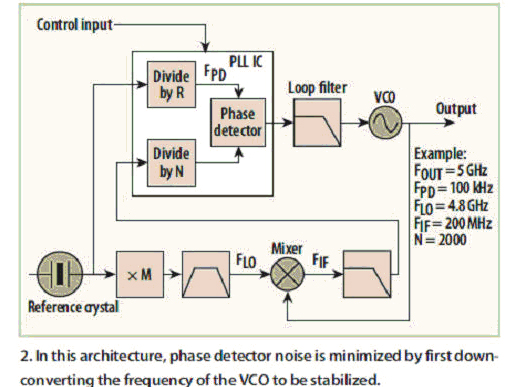

雖然不是專門用于這樣的設(shè)計,但為更常見應(yīng)用開發(fā)的PLL和DDS類型器件通常可以用作更為復(fù)雜、更高性能架構(gòu)中的構(gòu)建模塊。圖2顯示了一個基于PLL的架構(gòu)例子,這種架構(gòu)完全可以用來提高相位噪聲性能。在這個例子中,VCO輸出在連接到頻率合成器IC輸入之前先下變頻到一個低得多的頻率。這樣需要的分頻比就降低了,從而減少了來自相位檢測器的噪聲貢獻。對于圖示所示例子來說,分頻比將從50000降低到2000,環(huán)路帶寬內(nèi)的相位本底噪聲極限將改善28dB到-103dBc。如果是寬帶應(yīng)用,可以采用多級下變頻電路,本振(LO)頻率則通過開關(guān)選擇以保持較低的N值。

圖2、在這種架構(gòu)中,通過先將待穩(wěn)定的VCO頻率進行下變頻可以最大限度地減小相位檢測器噪聲。

架構(gòu)的改變在取得快速頻率切換時間時也非常有用。PLL穩(wěn)定到一個新頻率所需的時間反比于環(huán)路帶寬。在簡單架構(gòu)中,對小的信道頻率間隔要求意味著使用窄的環(huán)路帶寬,這將導(dǎo)致環(huán)路的頻率步長穩(wěn)定時間變慢。在基于整數(shù)PLL的設(shè)計中,參考頻率將等于這個頻率步長,而且環(huán)路帶寬必須比這個步長小大約一個數(shù)量級。在基于小數(shù)N的設(shè)計中,雖然參考頻率可以保持高得多的值,但環(huán)路濾波器通常仍然必須對落在步長倍數(shù)處的信號進行高衰減,從而對環(huán)路帶寬設(shè)置了一個上限。然而,通過將DDS用作PLL內(nèi)的高頻參考源,分頻比可以保持低值(這樣可以最大限度地減小噪聲),同時無需約束環(huán)路帶寬就能實現(xiàn)非常小的頻率步長。

現(xiàn)代DDSIC可以用很小的外形封裝產(chǎn)生甚高頻(VHF)范圍內(nèi)的輸出,并且具有MHz級的調(diào)諧步長和優(yōu)秀的相位噪聲。頻率和相位調(diào)制功能通常也包含在內(nèi)。近端雜散信號電平取決于相位查找表分辨率和輸出數(shù)模轉(zhuǎn)換器(DAC),而且一般都非常好(約-80dBc);然而,在輸出端會呈現(xiàn)電平很高的其它取樣信號。通過將DDSIC用作PLL中的頻率參考源,輸出頻率可以轉(zhuǎn)換成需要的任何頻率,多余的取樣信號也可以被PLL高效地濾除。圖3顯示了這種架構(gòu)的例子。

圖3、在這種方法中,DDS用作鎖相環(huán)合成器中的頻率參考源。

PLL可以認(rèn)為是提供跟蹤濾波功能,這是很有益的,因為它能極大地衰減DDS輸出端的多余取樣信號以及由下變頻過程產(chǎn)生的其它信號。根據(jù)可以容忍的雜散信號電平,可以要求PLL對電平已經(jīng)很低的近端雜散信號進行少許衰減或不做額外衰減。這樣,PLL的環(huán)路帶寬可以保持比傳統(tǒng)PLL合成器中的實際帶寬大許多,從而提高頻率切換速度。PLL參考頻率可以做得比DDS頻率步長高出許多,分頻比則非常小,從而實現(xiàn)優(yōu)異的相位噪聲性能。由于更大的環(huán)路帶寬等同于特定偏移處更大的環(huán)路增益,而且來自相位檢測器的噪聲貢獻更低,因此VCO貢獻的噪聲成份也可以得到有效降低。

值得注意的是,對這種架構(gòu)中的頻率規(guī)劃細(xì)節(jié)必須仔細(xì)斟酌。參考振蕩器、DDS時鐘源和PLL參考源的頻率必須相對于要求的信道間隔加以仔細(xì)選擇,以便最大限度地降低所需參考發(fā)生硬件的復(fù)雜性,避免產(chǎn)生不能被濾除的近端雜散信號。

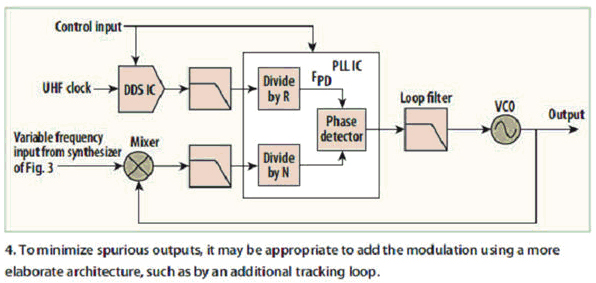

如上所述,許多DDSIC具有頻率和相位調(diào)制功能,而這些功能可能在要求調(diào)制后輸出的場合用得到,例如產(chǎn)生頻率調(diào)制連續(xù)波(FMCW)雷達(dá)系統(tǒng)要求的線性頻率斜坡場合。在實際應(yīng)用中,為了盡量減少雜散信號輸出,最好是增加使用更精巧架構(gòu)的調(diào)制電路,比如通過額外的跟蹤環(huán)路,如圖4所示。

圖4、為了盡量減少雜散輸出,正確的做法是增加使用更加精巧架構(gòu)的調(diào)制電路,比如通過額外的跟蹤環(huán)路。

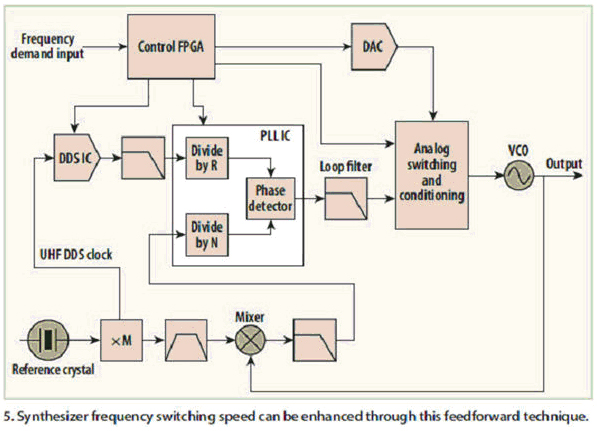

特別是在寬帶系統(tǒng)中,通過使用前饋技術(shù)可以極大地提高頻率切換速度,案例見圖5。當(dāng)接收到一個改變頻率的命令時,環(huán)路被斷開,VCO控制電壓隨后受DAC的控制,并到達(dá)一個預(yù)期對應(yīng)所需新輸出頻率的值。接著環(huán)路再次閉合,同時PLL開始消除任何殘留的相位與頻率誤差。在實際應(yīng)用中,控制電壓會很快調(diào)整到接近要求的值,而且由于PLL只需消除很小的殘留誤差,因此系統(tǒng)總的穩(wěn)定時間將得到顯著縮短。注意,除了加快穩(wěn)定過程外,這種安排實際上在環(huán)路中使用許多頻率轉(zhuǎn)換級的寬帶系統(tǒng)中已被證明是非常有用的,而如果不這樣做的話,PLL可能沒有足夠的捕獲帶寬來穩(wěn)定大的步長。為了實現(xiàn)信道改變過程中嚴(yán)格受控的時間順序,控制邏輯功能最好由FPGA來完成。在實際使用時,對于擁有串行控制接口的器件來說,寫入要求的寄存器數(shù)據(jù)所需的時間可能是決定可以實現(xiàn)的切換時間中最重要的因素。

圖5、通過這種前饋技術(shù)可以提高合成器的頻率切換速度。

基于上述技術(shù)的實用微波頻率合成器可以同時實現(xiàn)低雜散信號電平、很快的切換速度和優(yōu)秀的相位噪聲,同時還能提供頻率調(diào)制(FM)和相位調(diào)制功能。通過仔細(xì)地選擇架構(gòu)和頻率規(guī)劃,同時在基于現(xiàn)場可編程門陣列(FPGA)的邏輯控制下使用現(xiàn)代PLL合成器和DDSIC,我們完全可以在高功效和高空間效率的封裝中實現(xiàn)這種高性能的設(shè)計(圖6)。

圖6、在FPGA控制的架構(gòu)中組合使用PLL和DDSIC能以高功效和高空間效率的封裝提供所需的性能等級。

粵公網(wǎng)安備 44030902003195號

粵公網(wǎng)安備 44030902003195號