作者:丁小汀

(北京交通大學電子信息工程學院北京100044)

摘要:直接數字頻率合成具有一系列優點,如頻率切換速度快、頻率分辨力高、頻率和相位易于控制等。DDFS可以產生各種所需要的波形。根據直接數字頻率合成的原理,利用80C51單片機、數/模轉換器DAC0832以及一些外圍電路設計了一種正弦波發生器。該系統電路設計簡單、頻率控制靈活,具有良好的實用性和可擴展性,不僅可用于正弦波的發生,還可根據存儲器中存放的不同波形數據,輸出其他波形。

關鍵詞:直接數字頻率合成;單片機;正弦信號;頻率控制

1 引言

頻率合成技術迄今已經歷了三代:直接頻率合成技術、鎖相環頻率合成技術、直接數字式頻率合成技術。直接數字式頻率合成(Direct Digital Frequency Synthesis,DDFS或DDS)是第三代頻率合成技術的標志,他的主要特點是計算機參與頻率合成,既可以用軟件來實現,也可以用硬件來實現,或二者結合。直接數字式頻率合成器的最大優點就是頻率切換的速度極快(可達幾微秒),并且頻率、相位和幅度都可控,輸出頻率穩定度可達系統時鐘的穩定度量級,易于集成化,更主要的是由于計算機參與頻率合成,故可充分發揮軟件的作用。雖然現有的專用DDFS芯片的功能也比較多,但控制方式卻是固定的,因此不一定是我們所需要的。本文利用80C51單片機、D/A轉換器以及一些外圍寄存器設計的直接數字頻率合成器,電路設計簡單、頻率控制靈活,具有良好的實用性,信號精度誤差也在允許范圍之內。

2 DDFS的基本原理和總體框圖

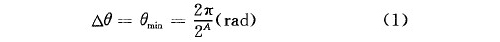

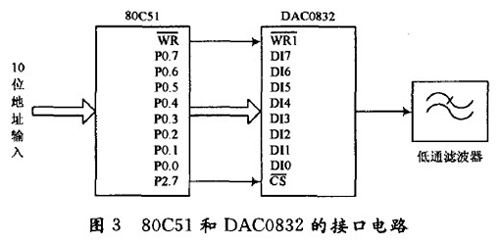

DDFS基本上由5部分組成,如圖1所示:頻率碼鎖存器(FR)、相位累加器(PA)、ROM(正弦表)、數/模變換器(D/A)、低通濾波器(LPF),他們在時鐘的統調下工作。首先,把一個單位幅度的正弦函數的相位在0~2 弧度內分成盡可能小的等間隔點,若用A位二進制數表示,分成2 個間隔點,則最小相位間隔應是:

算出相應相位點的單位正弦函數值,并用D位二進制數表示,寫入有A位地址線、D位數據線的ROM 中,構成一個所謂正弦表。合成頻率的過程是控制改變相位增量(即相位跳過的最小相位間隔的數目),由于相位增量不同,在一個正弦周期內的取樣點就不同,而取樣是在系統時鐘控制下進行的,即取樣周期是一定的,這樣,根據相位增量的累加和所對應的點(代表相位值)從ROM 中讀出相應的函數值所形成的量化正弦波的周期也隨相位增量的改變而改變,從而達到合成所需頻率的目的。

在圖1中,相位累加器根據頻率碼鎖存器中的頻率碼k每個時鐘累加一次,其輸出一方面(N位)回到加法器的另一個輸入端作為下一次累加的被加數,另一方面(A位)作為ROM 的地址碼對R0M 尋址,讀出相應的正弦函數值(二進制代碼),經過數據緩沖器穩定之后送到D/A變換器,得到一個幅值對應于PA輸出相位點的正弦函數值。下一個時鐘到來,累加器再增加一個k值,ROM 同樣讀出累加器輸出的A位地址碼所對應的正弦值,再送至D/A變換器。如此下去,相位累加器輸出值是一個階梯式的,相應地,D/A 的輸出是一個以正弦為包絡的階梯波。相位累加器的溢出正好對應著階梯正弦波的一個周期結束,再開始下一個周期。經低通濾波器的平滑濾波得到頻率為,f0的正弦波。由于時鐘周期Tc= (1/fc)是定值,而且是高穩定的,所以輸出頻率亦很穩定。

頻率分辨率為:

輸出頻率為:

式中N為相位累加器的位數,k為頻率碼。如果N=A,設定的k就是每個時鐘PA所跳過的最小相位間隔數。N 的增加意味著頻率分辨率的提高,但是A的增加卻意味著ROM 容量的增加,使設備復雜化,故一般N> A。本設計中的參數設置:N =12,A =10,D=8。

3 系統主要功能模塊的具體實現

3.1 頻率碼鎖存器(FR)、相位累加器(PA)

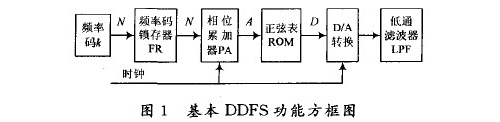

如圖2所示,頻率碼鎖存器由2片8位D型鎖存器74LS373構成,第Ⅱ片只使用D0~D3 ,形成12位的頻率碼。相位累加器由3片4位全加器74LS283構成,形成12位的加法器。加法器的輸出經過2片寄存器74LS273后一方面(12位)反饋到全加器的輸入端作為被加數,另一方面(10位,舍棄低2位)作為地址碼對ROM 尋址,而頻率碼鎖存器輸出的頻率碼k作為加數。此處寄存器74LS273主要起數據緩沖的作用,他們都是在時鐘上升沿作。

3.2 ROM 正弦表

R0M正弦表用單片機80C51內部的程序存儲器來實現。由于相位累加器輸出的地址A是10位,而每個正弦函數值用8位二進制數來表示,所以正弦表的容量是1 kB。80C51的片內程序存儲器容量為4 kB,完全足夠,因此不用再擴充片外程序存儲器了。用80C51的P3.1,P3.0以及P1.7~P1.0作為10位地址的輸入口,用查表程序根據地址讀出相應的函數值,再由P0口輸出,送至D/A轉換。

所謂查表法,就是預先將滿足一定精度要求的表示變量與函數值之間關系的一張表求出,然后把這張表存于單片機的程序存儲器中。這時自變量為單元地址,相應的函數值為該地址單元中的內容。在微機應用系統中,一般使用的表均為線性表,他是一種最常用的數據結構,是個數據元素a1 ,a2,?a n的集合,各元素之間具有線性的位置關系。每次查表時,首先將P3.1,P3.0以及P1.7~P1.0,輸入的10位地址存放在20H,21H兩個單元中(高字節在20H),他將作為查表時的地址偏移量(函數值存放在程序存儲器的實際地址=表首地址+偏移量)。

3.3 數/模轉換器(D/A)

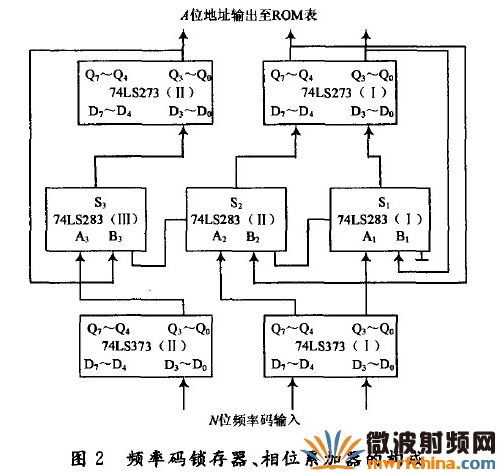

數/模轉換器DAC0832輸入數字量是8位,參考電壓V 的工作范圍是一10~+10 V,通過他將外加高精度電壓源與內部的電阻網絡相連接。芯片內有一個8位輸入寄存器和一個8位DAC寄存器,形成兩級緩沖結構。這樣可使DAC轉換輸出前一個數據的同時,將下一個數據傳送到8位輸入寄存器,以提高數/模轉換的速度。DAC0832與80C51的接口電路如圖3所示,80C51的P0口直接與DAC0832的數字輸入DI7~DI0相接,8OC51的WR與DAC0832的WR1相接,P2.7與片選端CS連接,芯片采用的是單緩沖方式。這時芯片的地址為7FFFH。

3.4 系統時鐘的產生

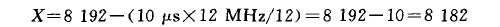

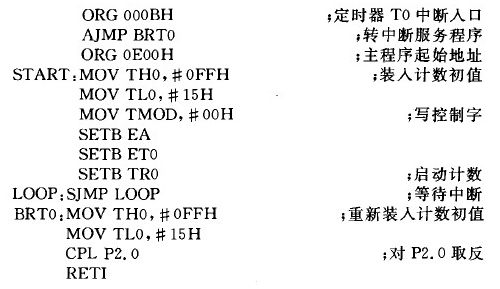

系統時鐘可利用80C51的定時/計數器產生。時鐘頻率要根據最高輸出頻率確定,一般fc≥ 4f0max ,而低通濾波器的截止頻率為最高輸出頻率。本設計中時鐘頻率要求為50 kHz,則要用定時器輸出周期為20 us方波。選用定時/計數器T0,工作于方式0,輸出為P2.0引腳。20us的方波可由間隔10us的高低電平相間而成,因而只要每隔10us對P2.0取反一次。由于實驗用80C51的時鐘頻率為12 MHz,因此計數初值:

4 軟件設計

4.1 ROM 查表程序

4.2 用定時器產生系統時鐘的程序

5 結語

經過示波器觀察可以看到清晰的正弦波形,通過計算機改變頻率碼k,可以得到不同頻率的波形,且輸出頻率隨頻率控制字的增大而增大。但輸出頻率超過13 kHz時,輸出波形明顯失真,這主要由D/A轉換、低通濾波等部分產生的雜散所致。由于DDFS采用全數字結構,不可避免地引人了雜散。其來源主要有3個:相位累加器相位舍位誤差造成的雜散,幅度量化誤差(由存儲器有限字長引起)造成的雜散和DAC非理想特性造成的雜散。

本文的設計是以產生正弦波為例,實際上只要在DDFS的波形存儲器存放不同的波形數據,就可以實現各種波形輸出,如三角波、鋸齒波和矩形波,甚至是任意波形。另外只要在DDFS內部加上相應控制,如調頻控制FM、調相控制PM 和調幅控制AM,即可以方便靈活地實現調頻、調相和調幅功能,產生FSK,PSK,ASK和MSK等信號。在通信、雷達、電子對抗、導航、廣播電視、遙控遙測、儀器儀表等領域具有廣泛的應用前景。

粵公網安備 44030902003195號

粵公網安備 44030902003195號