頻率源是現(xiàn)代短波射頻通信系統(tǒng)的核心,對整個系統(tǒng)的正常運(yùn)行起著決定性的作用。作為射頻電路與系統(tǒng)的核心設(shè)備,頻率源的好壞關(guān)系著整個系統(tǒng)的穩(wěn)定性。現(xiàn)在的頻率合成技術(shù)正朝著雜散和相位噪聲更低的方向發(fā)展,同時還要求有更寬的頻帶和更高的頻率分辨率。直接數(shù)字頻率合成(DDS)正是在這種需求背景下發(fā)展起來的,它具有極微小的頻率調(diào)諧和相位分辨能力。融合了模擬和數(shù)字技術(shù)的DDS是產(chǎn)生高質(zhì)量、高頻譜純度、寬頻帶頻率的理想方法。文中基于ADI公司的AD9912芯片提出一個直接頻率合成方案,輸出頻率范圍為46.5~75MHz.

1 DDS基本工作原理

直接頻率合成器DDS本質(zhì)上是一種高分辨率的數(shù)字分頻器。通過頻率調(diào)節(jié)字來分頻系統(tǒng)時鐘,以輸出所需的頻率。DDS有兩個顯著特點(diǎn):(1)DDS工作在數(shù)字域,其輸出頻率、相位和幅度可以在數(shù)字處理器的控制下,精確而快速地變換;(2)其頻率分辨率主要取決于頻率調(diào)節(jié)字的位數(shù),可以達(dá)到極高的頻率分辨率。

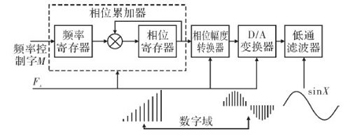

典型的DDS原理框圖如圖1所示。它主要包括:相位累加器,相位-幅度變換器,數(shù)/模變換器和低通濾波器。

圖1 典型的DDS原理框圖

(1)相位累加器。

對于正弦波而言,雖然幅度不是線性的,但其相位卻是線性變化的,這正是DDS能夠合成正弦波的基礎(chǔ)。DDS根據(jù)頻率調(diào)節(jié)字的位數(shù)N,把0°~360°的相位變化平均分成2N等份。假設(shè)系統(tǒng)參考時鐘為fs;輸出頻率為fout.在每個時鐘周期轉(zhuǎn)過一個角度360°/2N,則可以產(chǎn)生一個頻率為fs/2N的正弦波的相位增量。因此,只需選擇恰當(dāng)?shù)念l率調(diào)節(jié)字M,使得fout/fs=M/2N,就可以得到所需的輸出頻率fout。

由式(1)可以得到DDS的最小頻率分辨率為

(2)相位幅度轉(zhuǎn)化器。

根據(jù)相位累加器的輸出,可以得到合成fout頻率所對應(yīng)的相位信息,相位幅度轉(zhuǎn)化器可以把累加器輸出的數(shù)字相位信息變換成相應(yīng)的幅度值。這個數(shù)值以二進(jìn)制的形式被送入DAC進(jìn)行數(shù)模轉(zhuǎn)換。此相位到幅度的轉(zhuǎn)換通過查表操作完成。

(3)D/A數(shù)模變換器。

從相位幅度轉(zhuǎn)換器得到的二進(jìn)制數(shù)字信號被送入數(shù)/模(D/A)轉(zhuǎn)換器中,變換成模擬信號輸出。此處D/A變換器的位數(shù)對輸出頻率的分辨率并沒有影響。輸出頻率的分辨率由頻率調(diào)節(jié)字的位數(shù)決定。

2 系統(tǒng)設(shè)計

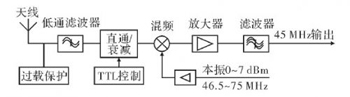

設(shè)計中采用低抖動、低雜散的直接數(shù)字頻率合成器DDS作為短波射頻通信系統(tǒng)的本振源。整個短波射頻系統(tǒng)的原理框圖如圖2所示。

圖2 短波射頻系統(tǒng)的原理框圖

設(shè)計采用ADI公司的高端產(chǎn)品AD9912.它最高支持1 GHz的采樣時鐘,并且內(nèi)置了一個14 bit的D/A變換器,支持48 bit的頻率調(diào)節(jié)字,最高頻率分辨率為4μHz.AD9912的突出特點(diǎn)是擁有能編程的輔助直接數(shù)字頻率合成器通道,可以降低輸出頻譜中諧波雜散的等級,改進(jìn)了DDS固有的雜散和噪聲大的缺點(diǎn)。

本設(shè)計中采用MSP430F2012單片機(jī)作為AD9912頻率輸出的控制器。在啟動DDS芯片前,首先要配置信號IO_UPDAte、PWRDOWN、HOLDOVER及S1~S4時鐘使能信號,使AD9912正常工作。DDS上電啟動后,單片機(jī)通過SDO、CSB、SCLK向AD9912寫入頻率調(diào)節(jié)字,輸出HSTL電平的時鐘信號。信號經(jīng)選擇和電平轉(zhuǎn)換后,經(jīng)過輸出驅(qū)動器輸出。

AD9912內(nèi)部集成了采樣時鐘倍頻器,即鎖相環(huán)(PLL)。在使用PLL的情況下,采樣時鐘源中的任何噪聲或雜散都會在PLL的環(huán)路帶寬以20lo gx關(guān)系被放大,x是頻率放大的倍數(shù)。由于輸入時鐘的雜散在輸出的相位噪聲會隨著輸出頻率不同而改變,在采樣時鐘相同的情況下,輸出兩個不同頻率時的相位噪聲關(guān)系為

從式(3)可以看出,在固定輸出頻率的前提下,盡量提高采樣時鐘速率可以提高輸出頻率的相位噪聲性能。在設(shè)計中,為達(dá)到最佳的性能,放棄了內(nèi)部PLL環(huán)路,而采用外部高性能PLL輸出的1GHz采樣時鐘。

2.1 外部環(huán)路濾波器設(shè)計

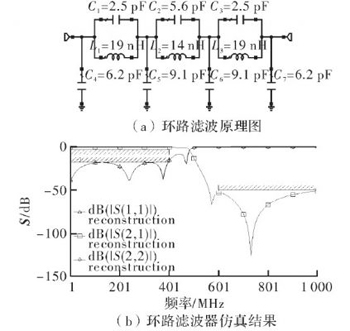

外部環(huán)路濾波可以將DAC輸出的雜波和鏡像頻譜濾掉,可以平滑輸出波形,對信號的輸出質(zhì)量有較好地改善作用。外部環(huán)路濾波器采用橢圓函數(shù)低通濾波器。電路設(shè)計時采用分立LC元件構(gòu)成截止頻率為400 MHz的低通濾器。電路原理及仿真結(jié)果如圖3所示。

圖3 環(huán)路濾波器的原理圖及仿真結(jié)果

2.2 編程控制

對AD9912編程是為了實現(xiàn)頻率的步進(jìn)控制,處理由外部控制輸入的頻率值,由單片機(jī)生成頻率調(diào)節(jié)字,經(jīng)SPI方式送入DDS中,合成系統(tǒng)所需的頻率。數(shù)據(jù)寫入時SCLK、SDI、CSB信號由單片機(jī)產(chǎn)生,寫入時序嚴(yán)格按照SPI協(xié)議進(jìn)行。

3 仿真及測試結(jié)果

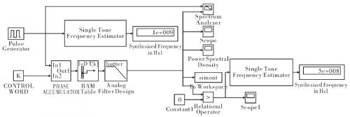

DDS輸出波形的仿真采用Matlab中的Simulink工具。根據(jù)DDS的工作原理及AD9912的數(shù)據(jù)手冊,可以建立AD9912在Simulink中的模型。AD 9912的Simulink模型如圖4所示。

圖4 AD 9912在Simulink下的仿真模型

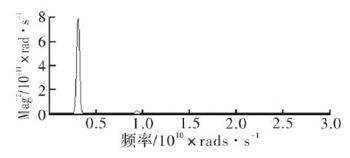

設(shè)置頻率調(diào)節(jié)字M=14073748835532后,得到DDS輸出信號的頻率為50 MHz,Simulink仿真功率譜密度如圖5所示。

圖5 M=14073748835532的功率譜密度分布圖

射頻短波通信系統(tǒng)中對頻率源的輸出的頻帶寬度要求為46.5~75 MHz,步進(jìn)頻率為50 kHz.AD9912的輸出分辨率為fDDS=f/248,本設(shè)計中采樣時鐘1 GHz,最小分辨率可達(dá)3.55μHz,完全可以達(dá)到設(shè)計指標(biāo)。圖6是安捷倫頻譜分析儀實測的DDS輸出信號頻譜圖。

圖6 DDS輸出信號頻譜圖

4 結(jié)束語

針對射頻短波通信系統(tǒng)中的頻率源要求,分析了整個頻率源的實現(xiàn)方法。搭建了單片機(jī)+DDS的實現(xiàn)方法,采用具有雜散抑制通道的新型DDS芯片AD9912,時鐘輸入采用外部低雜散高性能的PLL信號,增加外部環(huán)路濾波網(wǎng)絡(luò),有效提高了輸出信號的質(zhì)量。通過對輸出信號的測試,驗證了該方案在輸出頻帶46.5~75 MHz內(nèi)具有相位噪聲小、頻率值精準(zhǔn)、頻率分辨率高等特點(diǎn),滿足短波射頻通信對頻率的指標(biāo)要求。

粵公網(wǎng)安備 44030902003195號

粵公網(wǎng)安備 44030902003195號