電信基站等設備需要多路供電電源,以滿足不同的輸出電壓、輸出電流要求。機房的主電源通常先被轉換為+48V或-48V直流電源,然后根據需要傳送到各個系統設備,最后再轉換成較低等級的電源電壓。

常見的設計方案是利用電源模塊或現成的轉換器(磚)將48VDC(或-48VDC)電源轉換到一個較低的電源電壓,然后再由電源模塊或PCB板上電路將其轉換為要求的各種電壓。一個典型例子是,從48V輸入轉換到8.5V,通常這個8.5V與48V輸入是電氣隔離的。

將8.5V電源分別轉換成用于RF功率放大器的7.5V(基站設備)和用于邏輯電路的5V、3.3/3V,或用于FPGA、處理器核的1.8V電壓。考慮到系統所要求的供電電流和功耗指標,采用開關模式降壓轉換技術從8.5V產生較低的電源,而對于RF級的7.5V電源則大多采用 低壓差線性穩壓器(LDO)實現,以滿足射頻電路的低噪聲要求。

線性穩壓器會根據輸出電壓的要求調整輸入與輸出的壓差,因而要消耗一定的功率(電流與輸入/輸出壓差的乘積),表現為調整管的熱耗。為了提高散熱能力,設計人員不得不折中考慮輸入/輸出壓差、功率耗散、調整管選擇等因素,以便在規定的負載電流和輸入電壓范圍內可靠地工作在線性區(非飽和、截止)。在本文介紹的電路中,輸入電源電壓隨著系統負載的變化量可能達到100mV,壓差可能達到900mV,由此可見,8.5V的電源電壓剛好滿足要求。本例中標稱壓差1V剛好能夠接受。

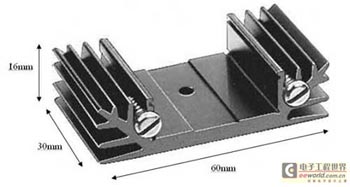

多數所謂的LDO其實際壓差會高于1V,因此這些器件需要輸入與輸出之間保持更大的壓差裕量。對于1V壓差,調整管上的功耗為1V×10A=10W。如此大的功耗要求系統提供合理的熱管理方案,并因此會增加小型散熱器及相關材料成本和裝配時間。如圖1所示,采用6.8ºC/W典型系數的散熱器(比如Aavid Thermalloy公司的散熱器)和TO-220封裝的的溫升將高出室溫68ºC左右(為簡化起見,忽略RθJC降額系數及其它熱阻的影響)。考慮到機架內部其它功率元件,其內部溫度通常要高于外部環境溫度,散熱片甚至可能工作在100ºC以上。為了保證系統可靠工作,這種情況下顯然無法使用更小的散熱片。

圖1:典型的6.8ºC/W散熱器。

設計中需要低RDS 場效應管(FET),以降低串聯調整管的壓降,從極性考慮要求使用P溝道器件。而具有相同架構的P溝道FET其導通電阻可能是N溝道FET導通電阻的兩倍以上,另外,P溝道FET的價格也比較高。

為便于比較,我們可以考察一下國際整流器公司(IR)的P溝道管IRF9Z34N和N溝道管IRFZ34,二者的擊穿電壓均為55V。100ºC時,P溝道器件的導通電阻為100mΩ,可承載12A電流;而N溝道器件的導通電阻僅為40mΩ,可承載電流為18A。P溝道器件的價格大約貴兩倍。

提供10A峰值電流時,P溝道FET的導通壓降是1V,而具有40mΩ RDSon的N溝道FET的導通壓降為400mV。另一種選擇是使用 PNP晶體管,但即使是這樣,集電極與發射極之間的飽和壓降也會達到200mV。還可以選擇性能超過雙極性技術的超低RDSon N溝道FET,但這種器件需要更高的柵極驅動電壓。如果能夠找到驅動超低RDSon N溝道FET的方法的話,上述問題將迎刃而解。

這也正是開關模式轉換器所面臨的一個設計挑戰,為了驅動超低RDSon N溝道FET,可以采用電壓自舉技術:將一個動態開關電壓通過二極管進行交流耦合,再對儲能電容充電,就可得到高于輸出電壓的N溝道FET柵極驅動電壓。如果電路板或電源模塊內含有降壓轉換器,則可利用其開關信號產生線性穩壓器所需的柵極驅動電壓。

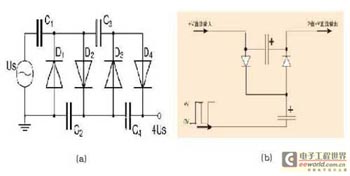

也就是說,我們可以將降壓轉換器的開關節點連接到簡單的倍壓電路。常見的倍壓電路是半波系列乘法器,也稱作維拉德(Villard)級聯電路(圖2)。幅度為±Us的交流電壓作用到該電路可以獲得4倍的輸出,即輸出端得到4Us。

開關電壓相對于地電平的擺幅為Us時,該電路可產生4Us的輸出,而降壓轉換器開關節點的擺幅大約為Vin至地電平。因此如果降壓轉換器的供電電壓為8.5V,則其進入電感的開關電壓為0V至+8.5V,得出Us=4.25V,如圖2所示。

圖2:(a) Villard級聯倍壓電路;(b) 倍壓電路輸入為+V,開關幅度為+V,產生2倍(+V)輸出。

如果考慮轉換器的占空比,則需作進一步的復雜計算,因為占空比與輸入、輸出電壓比和負載有關,為便于討論,我們假設占空比為50%,可以利用圖2電路獲得大約17V的電壓。需要輸出更高電壓時,可以級聯更多的倍壓單元電路,一級倍壓使用兩個二極管和兩個電容,可產生低電流直流輸出(圖2a)。

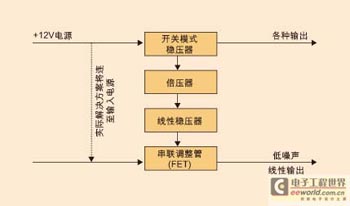

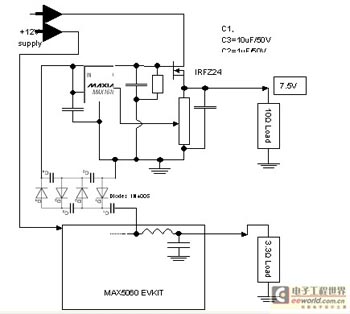

我們可以將上述電路產生的17V DC應用到一個簡單的低電流線性穩壓器(如MAX1616),目的是為低RDSon N溝道FET提供柵極驅動。FET器件采用8.5V供電,輸出7.5V為RF放大器供電,通過電位器分壓反饋網絡調節線性穩壓器輸出。該電路利用MAX5060評估板、MAX1616線性穩壓器、N溝道功率MOSFET以及相關的其它元件進行了測試,簡化原理圖如圖3所示,實際電路如圖4所示。

圖3:零壓差穩壓電路框圖。

電路工作原理

MAX5060EVKIT降壓轉換器可產生3.3V電壓,輸出電流達20A,開關頻率約為270kHz,由12V輸入產生3.3V輸出。由于圖4電路工作在輕載條件下,負載電流只有1A,作用在電感上的電壓波形占空比為25%,擺幅介于地電平和12V之間。利用該開關電壓驅動倍壓電路,可以在線性穩壓器(MAX1616)的輸入端得到大約24V的直流電壓。實際倍壓輸出為22.7V,能夠為線性穩壓器提供足夠的驅動。線性穩壓器的輸出可驅動低RDSon N溝道FET(IRFZ24N)的柵極。

利用一個可調電源為場效應管供電,從而允許根據輸入、輸出電壓的范圍調節壓降。FET的柵極由MAX1616 LDO的22V輸出驅動,并在分壓網絡R1的電壓達到1.24V之前始終將場效應管驅動在導通狀態,隨后關閉FET驅動器,使穩壓器保持平衡。

電阻R2和電容C2通過抑制高速瞬態響應和噪聲來控制環路的動態特性。電阻R2還可作為線性穩壓器的自身負載吸收FET關閉時的電流。通過選擇分壓網絡的電阻比設置輸出電壓值。在該應用中,R1選用250kΩ電位器,因此能讓MAX1616的輸出擺幅從1.25V上升到22V以上。

在不同輸入電壓、負載下觀察FET柵極驅動電壓的跌落測量壓差,由此確定電路進入閉環控制的工作點。一旦柵極驅動跌落到MAX1616 LDO所能提供的22V以下,電路將進入穩壓調整狀態。測量調整管兩端的輸入、輸出電壓之差,可以確定電源電壓、負載變化范圍內的壓降。

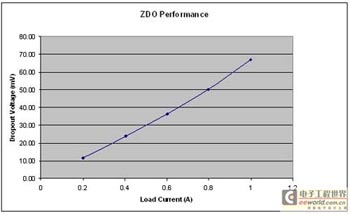

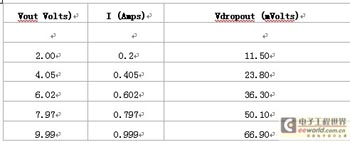

這種方法已經被證明是確定線性調整管壓降的行之有效的途徑,它從側面反映了MOSFET的RDSon,圖5以表格和圖形的方式給出了對該電路的性能測試結果。

本文小結

圖4所示電路提供了一個零壓差穩壓器(ZDO),可利用N溝道、低RDSon FET實現,MOSFET的柵極通過倍壓電路驅動。降低輸出負載會減小輸入、輸出之間的壓差,空載時達到零。大電流應用中,該電路能夠降低穩壓過程中的調整管損耗,進而降低對散熱器及其他熱管理技術的要求。

圖4:零壓差(ZDO)電路原理圖。

基站系統的LDO要求1V的壓差裕量,采用ZDO可大大降低這一裕量,對于需要10A輸出電流的應用,可以選擇具有極低RDSon的場效應管IRF1324,其RDSon低于1mΩ,利用該FET構建的ZDO理想情況下的壓差為每安培1mV。

在本文提供的例子中,所使用的FET即使在最糟糕的工作條件下也能有效降低調整管的功耗,考慮到負載變化及其他因素的影響,只需100mV的壓差裕量,再加上FET RDSon需要的10mV壓差,可以將原來的8.5V中間電壓降至7.61V。總壓差為110mV,10A電流對應的功耗為1.1W,節省大約9W的功率。利用表面貼裝器件可直接通過PCB的覆銅區域散熱,因此可以很容易解決熱管理問題。總之,使用IRF1324可省去散熱器,降低成本,簡化安裝過程,并為系統節省9W的能耗。

圖5:圖4所示ZDO電路的測試結果。

ZDO還可用于電池供電系統,系統所能提供的壓差裕量會隨著電池的工作電壓而發生顯著變化,ZDO在這樣的系統可有效延長電池的工作時間。

表1:零壓差穩壓器電路的主要性能。

本電路只是原理電路,只在直流輕載下進行過測試。讀者可以對其作進一步的開發,以優化動態負載響應及低輸入/輸出壓差特性。

粵公網安備 44030902003195號

粵公網安備 44030902003195號