網(wǎng)站首頁 > 資訊 > 新品發(fā)布 >

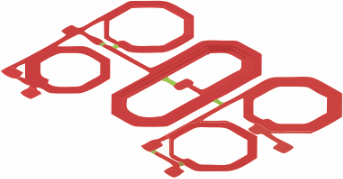

芯禾科技(Xpeedic)發(fā)布射頻芯片設(shè)計(jì)驗(yàn)證工具IRIS 2018

芯禾科技近日宣布,正式發(fā)布旗艦芯片電磁場仿真軟件IRIS 2018版本。

IRIS 2018 獲得了Globalfoundirs 22FDX工藝認(rèn)證,具有多核和分布式并行化的快速3D矩量法求解器,能顯著減少EM仿真的時間,幫助工程師實(shí)現(xiàn)設(shè)計(jì)效率的提高。軟件與Virtuoso的無縫集成,不僅使設(shè)計(jì)人員能夠簡單地在Cadence設(shè)計(jì)環(huán)境中執(zhí)行EM仿真、避免了手動和易出錯的layout數(shù)據(jù)轉(zhuǎn)換,而且還通過反標(biāo)實(shí)現(xiàn)了設(shè)計(jì)驗(yàn)證前后端的完美融合。

What’s new in IRIS 2018

· 支持先進(jìn)節(jié)點(diǎn)工藝文件中所定義的bias table和rho table,從而將電導(dǎo)率和實(shí)際金屬線寬隨著版圖中寬度和間距變化影響考慮在內(nèi)。· 在IRIS前端支持過孔合并功能,避免每次仿真iCell過孔重復(fù)合并操作,而且合并算法效率提升10倍。

· 作為Xpeedic和Ansys軟件合作計(jì)劃一部分,支持將IRIS的仿真項(xiàng)目導(dǎo)出到HFSS 3D Layout,并且自動優(yōu)化HFSS 3D Layout各項(xiàng)仿真設(shè)置以確保仿真精度。

· 統(tǒng)一IRIS2HFSS和IRIS2HFSS3DLayout兩種功能的導(dǎo)出界面,以簡化仿真項(xiàng)目互導(dǎo)流程。

· 基于用戶自動以的pin位置信息,自動查找并添加IRIS的仿真端口,以簡化用戶使用流程。

· 支持Synopsys StarRC Interconnect Technology Format (*.itf)工藝文件導(dǎo)出到IRIS Technology (*.lyr)文件.

· 簡化IRIS仿真設(shè)置和使用流程,從而帶來更好的用戶體驗(yàn)。

粵公網(wǎng)安備 44030902003195號

粵公網(wǎng)安備 44030902003195號