安捷倫科技公司(NYSE:A)在DesignCon上展示增強的PCI Express® 3.0 接收機特性測試解決方案。

Agilent PCIe® 3.0 接收機特性測試解決方案可以提供完整、精確的接收機容限測試結果,同時最大程度地減輕研發人員的工作量。新型J-BERT 軟件(版本7.40)在對PCIe 3.0 接收機設計進行測試時,可以調整128b/130b 編碼后的填充符的長度(又稱為SKP 有序集,用于補償收發端的時鐘差異)。

借助安捷倫測試儀,半導體和計算機領域中的設計與測試工程師能夠精確地表征和驗證在ASIC、插卡和主板中的PCIe 接收機端口是否符合標準。

自從PCI Express 版本3.0 發布以后,8 GT/s 接口被應用到多個計算機平臺。PCIe 設計一般使用公共參考時鐘,但是越來越多的設計現在要求使用具有獨立擴頻時鐘(SSC)的參考時鐘體系結構,例如通過電纜連接的PCIe 鏈路。當使用獨立的參考時鐘時,設計人員需要對發射端和接收端之間的時鐘速率差值進行補償,以避免緩沖區溢出。即使主板上是使用公共參考時鐘,當存在SSC 或使用乘法鎖相環時,也需要進行時鐘補償。根據PCI Express 標準的規定,是通過在正常的SKP 有序集中添加(或移除)SKP 符號來實現這種補償。

在接收端測試中,當環回模式中的被測器件改變了SKP 有序集長度時,新型Agilent J-BERT N4903B 高性能串行比特誤碼率測試儀軟件仍可以執行接收機測試。J-BERT 誤碼檢測器在統計誤碼數量時可以忽略SKP 有序集,即使有序集的長度不符合碼型發生器發出信號里的初始長度。在做調試時,工程師還可通過誤碼儀里的誤碼檢測器來監測SKP 有序集的計數。

安捷倫數字光學測試部門的戰略產品規劃師Michael Fleischer-Reumannr 表示:“安捷倫解決方案能夠處理PCIe 3.0 SKP 有序集在接收機抖動容限表征過程中的長度變化,這一優勢填補了PCIe 3.0 芯片組和電路板設計人員的需求空白。J-BERT 提供靈活的體系結構,融合了安捷倫在PCI Express 接收機測試方面的專業經驗,使我們足以應對新興的測試挑戰。”

借助這個增強型解決方案,安捷倫進一步完善了其完整、精確的PCIe 3.0 接收機測試解決方案,使其根據基本規范和卡機電規范進行表征。

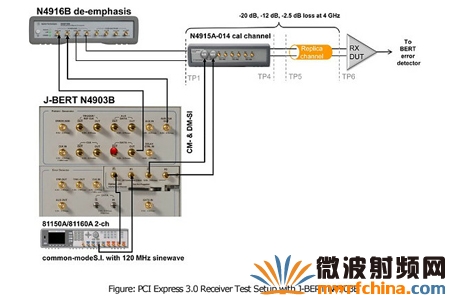

安捷倫接收機測試解決方案包括J-BERT N4903B 高性能串行BERT、N4916B 去加重信號轉換器、N4915A-014 PCIe 3.0 一致性校準通道、81150A 或81160A 脈沖函數任意噪聲發生器、Infiniium 90000 或90000 X 系列高性能示波器、N5990A-101 和N5990A-301 測試自動化和鏈路訓練軟件。N4880A 參考時鐘倍頻器可用于主板測試。

Agilent PCIe 3.0 接收機表征解決方案的優勢在于:

• 在統計誤差數量時可以忽略SKP 有序集的長度變化,從而對具有公共參考時鐘和單獨參考時鐘的PCIe 接收機進行測試。

• 通過啟用壓力信號校準軟件、可調節的前光標和后光標去加重、J-BERT 內置PCIe 3.0 一致性抖動和正弦干擾源、周期抖動掃描功能、100-MHz 參考時鐘倍頻器以及PCIe 3.0 一致性校準通道,可獲得精確且可重復的接收機測試結果。

• PCIe 3.0 壓力信號校準和接收機自動化測試軟件以及PCIe 3.0 鏈路訓練套件能夠控制J-BERT 中的碼型序列發生器,使被測器件進入環路模式,從而提高研發效率。

• 通過擴展,可對多種Gbit量級的總線應用進行精確特性測試(例如USB、SATA、MIPI M-PHY、TBT 和QPI),從而能夠保護您的投資。

安捷倫將在DesignCon 2013 上展示PCI Express 3.0 增強型接收機表征解決方案(展位201)。本屆展會于1 月28 日至31 日在圣克拉拉會議中心舉辦。安捷倫將提供廣泛的高速數字解決方案,其中一些主要工具可用于查明問題、優化器件并且交付設計與仿真結果。

安捷倫數字測試標準計劃

安捷倫數字測試標準計劃的專家積極參加各個國際標準組織,其中包括電子器件工程聯合會、PCI-SIG®、視頻電子標準協會、串行ATA 國際組織、串行連接SCSI(T10)、USB 應用廠商論壇、MIPI 聯盟、以太網標準(IEEE 802.3)、光互聯論壇等等。安捷倫積極參與這些標準組織的活動,以便安捷倫能夠在客戶需要時將適當的解決方案推向市場。

粵公網安備 44030902003195號

粵公網安備 44030902003195號